## **IBM Research Report**

# Laterally-Scaled Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> n-MODFETs with $f_{max}$ over 200 GHz and Low Operating Bias

S. J. Koester, K. L. Saenger, J. O. Chu, Q. C. Ouyang, J. A. Ott, K. A. Jenkins, D. F. Canaperi, J. A. Tornello, C. V. Jahnes, S. E. Steen

IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598

Research Division Almaden - Austin - Beijing - Haifa - India - T. J. Watson - Tokyo - Zurich

LIMITED DISTRIBUTION NOTICE: This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publication, its distributionoutside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g. payment of royalties). Copies may be requested from IBM T. J. Watson Research Center, P. O. Box 218, Yorktown Heights, NY 10598 USA (email: reports@us.ibm.com). Some reports are available on the internet at <a href="http://domino.watson.ibm.com/library/CyberDig.nsf/home">http://domino.watson.ibm.com/library/CyberDig.nsf/home</a>

### Laterally-Scaled Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> n-MODFETs with $f_{max} \ge$ 200 GHz and Low Operating Bias

S. J. Koester, Senior Member, IEEE, K. L. Saenger, J. O. Chu, Q. C. Ouyang, Member, IEEE, J.

A. Ott, K. A. Jenkins, Senior Member, IEEE, D. F. Canaperi, J. A. Tornello, C. V. Jahnes, and S. E. Steen

IBM T. J. Watson Research Center, Yorktown Heights, NY 10598 USA phone: 914-945-3605; fax: 914-945-2426; e-mail: skoester@us.ibm.com

#### ABSTRACT

We report on the dc and rf characterization of laterally-scaled, Si/SiGe n-MODFETs. Devices with  $L_g = 80$  nm and  $L_{ds} = 300$  nm had  $f_T = 80$  GHz and  $f_{max} = 210$  GHz. Separate devices with  $L_g = 70$  nm also had  $f_T$  values as high as 92 GHz. The MODFETs displayed enhanced  $f_T$  at reduced drain-to-source voltage,  $V_{ds}$ , compared to Si MOSFETs with similar  $f_T$  at high  $V_{ds}$ .

Index Terms: Silicon germanium, high mobility, MODFET

#### I. INTRODUCTION

SiGe MODFETs are attractive devices for future rf and mixed-signal communications applications, where low cost and compatibility with CMOS logic circuits are required. MODFETs offer the potential for high-speed [1] and low-power operation [2], as well as low noise [3] both at high and low frequencies. In the past, MODFETs have demonstrated performance improvement compared to Si MOSFETs with similar gate lengths [4]-[5]. Recently, however, Si MOSFET scaling has outpaced that of MODFETs. Si MOSFETs with gate lengths < 10 nm [6] and  $f_T$  over 200 GHz have been reported [7], while it has only been recently that sub-100 nm gate-length SiGe MODFETS have been demonstrated [8]-[10]. In this paper, we report on the dc and rf results of Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> n-MODFETs with gate lengths as small as 70 nm. The devices display record  $f_T$  and  $f_{max}$  values for SiGe MODFETs, including  $f_{max}$ values over 200 GHz, and show enhanced rf operation at low drain-to-source voltage compared to MOSFETs with similar  $f_T$  at high drain bias.

#### **II. DEVICE FABRICATION**

The modulation-doped heterostructure used in this work was grown on an 8" Si wafer by ultra-high vacuum chemical vapor deposition (UHV-CVD). The as-grown layer structure consisted of a relaxed Si<sub>1-x</sub>Ge<sub>x</sub> buffer layer, step-graded from x = 0 to a constant Ge composition of x = 0.3, a 9 nm strained Si quantum well, a 5 nm Si<sub>0.7</sub>Ge<sub>0.3</sub> spacer layer, an 8 nm phosphorous-doped n-type Si<sub>0.7</sub>Ge<sub>0.3</sub> supply layer and finally a 2 nm n-Si capping layer. The room-temperature electron sheet density was 2.2 x 10<sup>12</sup> cm<sup>-2</sup>, with a corresponding Hall mobility of 1700 cm<sup>2</sup>/Vs.

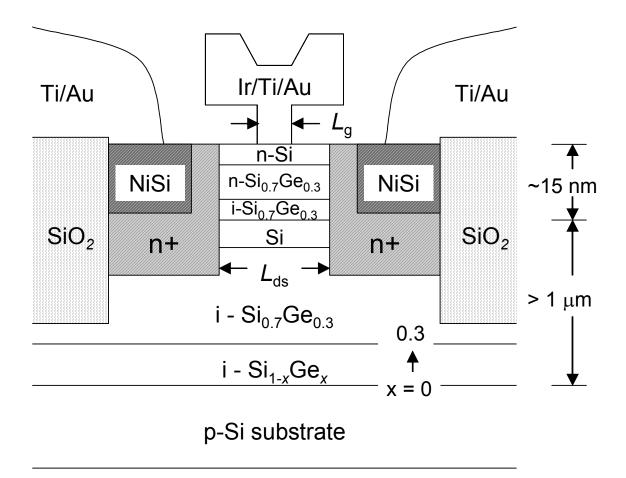

A schematic cross-sectional diagram of the device structure is shown in Fig. 1. The fabrication started with the formation of SiO<sub>2</sub>-filled shallow-trench isolation regions. Next, resist openings were patterned, and after a Ge pre-amorphization implant, phosphorous ions were implanted with a dose of 5 x  $10^{15}$  cm<sup>-2</sup> and an energy of 12 keV. The implants were then activated by rapid thermal annealing at 700 °C for 1 minute. The drain-to-source spacing, Lds, defined as the distance between the drain and source implants, was kept at a constant value of 300 nm. Next, non-self-aligned silicide regions were formed by depositing SiO<sub>2</sub> and TiN, patterning resist and then etching the TiN in the patterned regions. Then, 12 nm of Ni and 20 nm of TiN were sputtered deposited and annealed at 500 °C for 1 minute. The unreacted Ni, as well as the TiN, were then removed using a selective etch. The NiSi regions were configured such that they were offset by 100 nm from the edge of the source and drain implants. After defining electron-beam alignment marks, T-shaped gates were formed by using electron-beam lithography to pattern PMMA/P(MMA/MAA) dual layer resist, followed by evaporation and lift off Ir/Ti/Au (20/20/240 nm) metal. Devices with gate lengths,  $L_g$ , ranging between 70 and 100 nm were fabricated. The top of the T-gate was kept at a constant width of 400 nm. The gate was not self-aligned to the source and drain, but no performance degradation was observed to result from minor misalignments. Finally, the process was completed by patterning and lifting off Ti/Au (20/350 nm) pad metallization.

#### **III. DC CHARACTERISTICS**

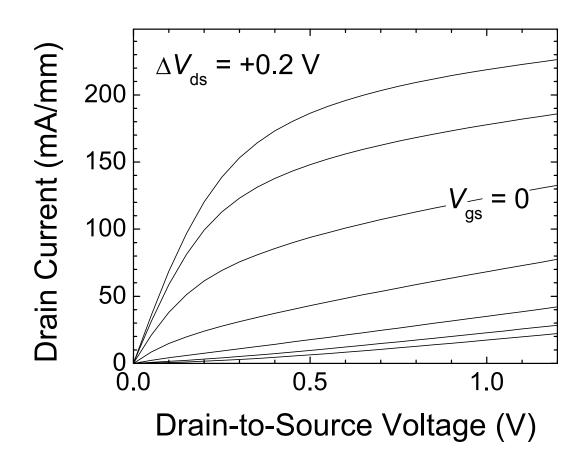

The dc output characteristics of a typical MODFET with  $L_g = 80$  nm and  $L_{ds} = 300$  nm are shown in Fig. 2. At a drain-to-source bias,  $V_{ds}$ , of +1 V, the device had a peak transconductance,  $g_{m}$ , of 286 mS/mm. The corresponding output conductance,  $g_d$ , was 48 mS/mm, leading to a dc voltage gain,  $A_v = g_m/g_d$ , of 6.0. The relatively high output conductance of these devices is due to the fact that no p-well doping was utilized. Significant improvement in  $A_v$  is expected by using a buried p-well layer, which can suppress the deep source-to-drain leakage current without degrading the channel mobility [11]. The gate leakage in these devices, on the other had, was very low. Despite the proximity of the gate to the source and drain implants, the gate current,  $I_g$ , at  $V_{ds} = +1$  V was 43  $\mu$ A/mm at  $V_g = -1$  V and only 1.2  $\mu$ A/mm at  $V_{gs} = -0.02$  V, the gate bias for peak  $g_m$ .

#### **IV. RF CHARACTERISTICS**

The rf characteristics were measured using devices configured in a two-finger pi-geometry, with total gate width,  $W_{\rm g}$ , of either 20 µm or 40 µm. An optimized gate pad geometry was used to eliminate resistance arising from the overlap of the pad metal with the T-gate metal [9]. S-parameter measurements were performed using an HP8510C network parameter analyzer, on both the active devices as well as open-circuit and short-circuit geometries. After *y*- and *z*-parameter de-embedding, the  $f_{\rm T}$  and  $f_{\rm max}$  values were determined by -20 dB/dec extrapolation of  $|h_{21}|^2$  and Mason's unilateral gain, MUG, respectively.

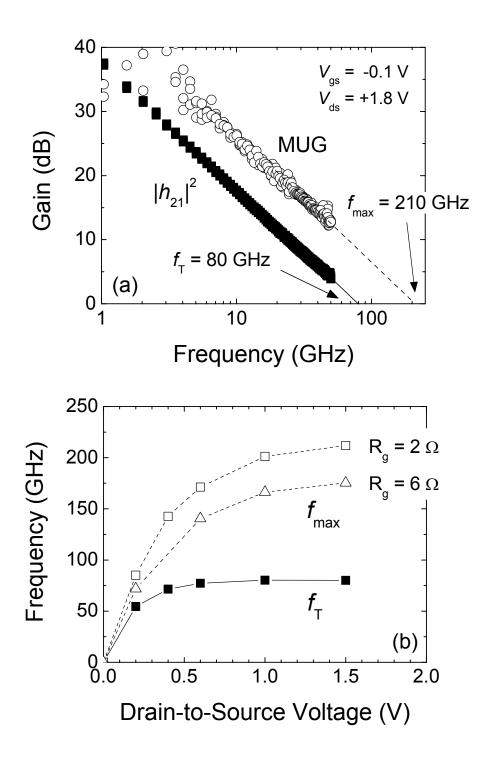

The results of the s-parameter analysis described above are shown in Fig. 3(a) for a 20 µmwide device with  $L_g = 80$  nm and  $L_{ds} = 300$  nm. The bias voltages were  $V_{gs} = -0.1$  V and  $V_{ds} =$ +1.8 V. The devices showed nearly ideal roll off behavior for both  $|h_{21}|^2$  and MUG, and extrapolated values of  $f_T = 80$  GHz and  $f_{max} = 210$  GHz were determined. To our knowledge, this is the first reported demonstration of a SiGe MODFET with  $f_{max}$  over 200 GHz. The drain bias dependence of  $f_T$  and  $f_{max}$  is shown in Fig. 3(b). Both  $f_T$  and  $f_{max}$  remain high at reduced drain bias; for instance, at  $V_{ds} = +0.4$  V, the extrapolated  $f_T$  and  $f_{max}$  values were 71 GHz and 143 GHz, respectively. The gate resistance was an important factor in achieving high  $f_{\text{max}}$ . For the device shown in Fig. 3(a),  $R_{\text{g}}$  was only 2  $\Omega$ , while previous devices with  $R_{\text{g}} = 6 \Omega$ , also shown in Fig. 3(b), had  $f_{\text{max}}$  of only 175 GHz [9].

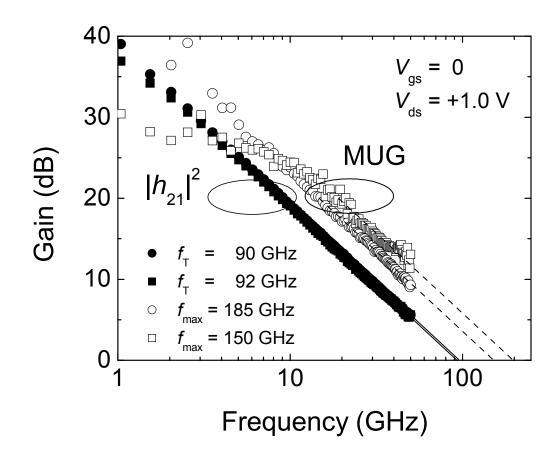

The RF measurement results for devices with  $L_g = 70$  nm are shown in Fig. 4. At bias conditions of  $V_{gs} = 0$  and  $V_{ds} = +1$  V, the device with  $W_g = 20 \ \mu\text{m}$  produced  $f_T$  and  $f_{max}$  values of 90 GHz and 185 GHz, respectively. At  $V_{ds} = +1.8$  V,  $f_{max}$  increased to 200 GHz, while  $f_T$ dropped to 85 GHz. The  $f_T$  increase compared to  $L_g = 80$  nm is attributed to the reduced gate capacitance, while the reduced  $f_{max}$  is likely due to the higher  $g_d$  at short gate length. The figure also shows the results for 70 nm gate-length devices with  $W_g = 40 \ \mu\text{m}$ . At  $V_{gs} = 0$  and  $V_{ds} =$ +1 V, these devices had slightly higher  $f_T$  of 92 GHz, but  $f_{max}$  decreased to 150 GHz, a direct result of the increased gate resistance in the wider device.

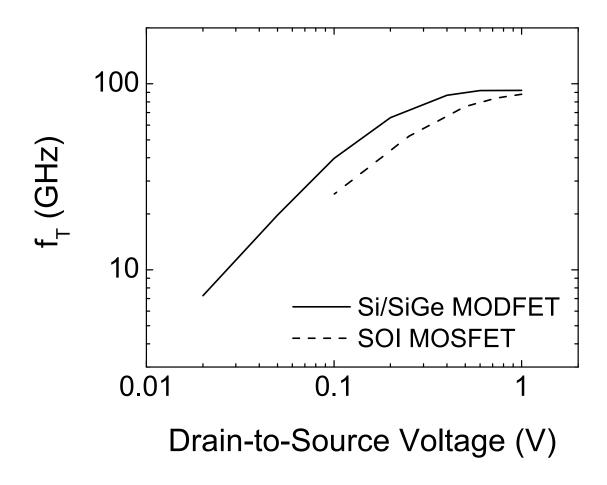

The 40 µm-wide devices described above were analyzed further to compare the biasdependence of  $f_{\rm T}$  with Si MOSFETs. The MOSFETs used for this study were partially-depleted SOI MOSFETs with  $W_{\rm g} = 16.8$  µm and  $L_{\rm poly} = 0.13$  µm. This gate length was chosen because it produced devices with an  $f_{\rm T}$  similar to that of the MODFETs at  $V_{\rm ds} = +1$  V. A plot of  $f_{\rm T}$  vs.  $V_{\rm ds}$ for the two devices is shown in Fig. 5. The plot shows that at reduced  $V_{\rm ds}$ , the MODFET produced significantly higher  $f_{\rm T}$  than the MOSFET. While the MODFET had only a 5% higher  $f_{\rm T}$ at  $V_{\rm ds} = +1$  V, at  $V_{\rm ds} = +0.25$  V, the MODFET  $f_{\rm T}$  was 30% higher, and at  $V_{\rm ds} = +0.1$  V, the improvement increased to 50%.

#### V. DISCUSSION AND CONCLUSIONS

The results described in this paper represent the first demonstration of SiGe MODFETs with  $f_{\rm max}$  over 200 GHz, and further demonstrate the potential of utilizing the high mobility that MODFETs offer for enhanced performance at low voltages. The results suggest that the observed  $f_{\rm T}$  improvement compared to Si MOSFETs at low drain bias is a direct result of the higher channel mobility, since MODFETs are predicted to reach velocity saturation at a lower lateral electric field [12]. However, the MODFET results reported here still fall short of the best Si MOSFET results [7], suggesting that considerable improvement of the MODFET device design is possible. Previous simulation results confirm this [13], and indicate that in order to achieve enhanced performance with reduced gate lengths, the MODFET layer structure needs to be scaled vertically. A shallower quantum well will reduce the effect of fringing capacitance effects that can degrade  $f_{\rm T}$ , and reduce the drain impact on the channel potential which leads to high output conductance. The low gate current of the present devices indicate that further vertical scaling of the layer structure should be possible before the gate-leakage limit is ultimately reached. In addition, the utilization of p-well doping, or a buried insulating layer [11] will also be useful to control output conductance and off-state leakage, and allow  $L_{ds}$  to be further reduced to minimize series resistance.

#### ACKNOWLEDGEMENTS

The authors would like to acknowledge the support of DARPA, under contract No. N66001-00-C-8086. The authors would like to acknowledge M. J. Rooks, R. A. Carruthers, and the MRL fabrication facility for technical support.

#### REFERENCES

- U. König, M. Glück, and G. Höck, "Si/SiGe field-effect transistors," *J. Vac. Sci. Technol. B*, vol. 16, pp. 2609-2614, 1998.

- [2] A. Vilches, K. Fobelets, K. Michelakis, S. Despotopoulos, C. Papavassiliou, T. Hackbarth, and U. König, "Monolithic micropower amplifier using SiGe n-MODFET device," *Electron. Lett.*, vol. 39, pp. 884-886, 2003.

- [3] M. Enciso, F. Aniel, P. Crozat, R. Adde, M. Zeuner, A. Fox, and T. Hackbarth, "0.3 dB minimum noise figure at 2.5 GHz of 0.13 μm Si/Si<sub>0.58</sub>Ge<sub>0.42</sub> n-MODFETs," *Electron. Lett.*, vol. 37, pp. 1089-1090, 2001.

- [4] U. König, A. J. Boers, F. Schäffler, and E. Kasper, "Enhancement mode n-channel Si/SiGe MODFET with high intrinsic transconductance," *Electron. Lett.*, vol. 28, pp.160-162, 1992.

- [5] K. Ismail, S. Rishton, J. O. Chu, K. Chan, and B. S. Meyerson, "High-performance Si/SiGe n-type modulation-doped transistors," *IEEE Elect. Dev. Lett.*, vol. 14, pp. 348-350, 1993.

- [6] B. Doris, *et al.*, "Extreme scaling with ultra-thin Si channel MOSFETs," in *IEDM Tech. Digest*, 2002, pp. 267-270.

- [7] N. Zamdmer, J. Kim, R. Trzcinski, J.-O. Plouchart, S. Narasimha, M. Khare, L. Wagner, and S. Chaloux, "A 243-GHz  $f_T$  and 208-GHz  $f_{max}$ , 90-nm SOI CMOS SoC technology with low-power millimeter-wave digital and RF circuit capability," in *Symp. on VLSI Tech.*, 2004, pp. 98-99.

- [8] M. Zeuner, A. Fox, T. Hackbarth, D. Behammer, and U. König, "90 GHz f<sub>T</sub> SiGe HFET with fully self aligned sub 100 nm gate," in *Proc. 60th Annual Dev. Res. Conf.*, 2002, p. 53.

- [9] S. J. Koester *et al.*, "80 nm gate-length Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> n-MODFET with 194 GHz f<sub>max</sub>,"

*Electron. Lett.*, vol. 39, pp. 1684-1685, 2003.

- [10] A. Kasamatsu, K. Kasai, K. Hikosaka, T. Matsui, and T. Mimura, "60 nm gate-length Si/SiGe HEMT," *Appl. Surf. Sci.*, vol. 224, pp. 382-385, 2004.

- S. J. Koester *et al.*, "High performance SiGe MODFET technology," in *Proc. Mat. Res.* Soc., 2004, vol. 809, pp. 171-179.

- [12] P. Dollfus, "Si/Si<sub>1-x</sub>Ge<sub>x</sub> heterostructures: electron transport and field-effect transistor operation using Monte Carlo simulation," *J. Appl. Phys.*, vol. 82, pp. 3911-3916, 1997.

- [13] Q. C. Ouyang, S. J. Koester, J. O. Chu, A. Grill, S. Subbanna, D. A. Herman, Jr., "A comprehensive simulation study of strained-Si/SiGe nMODFET scaling for RF applications," in *Proc. IEEE Intern. Conf. on Simulation of Semicond. Proc. and Dev. (SISPAD)*, 2002, pp. 59-62.

Figure 1. Cross-sectional diagram of the completed Si/SiGe n-MODFET device structure.

Figure 3. (a) De-embedded  $|h_{21}|^2$  and MUG plotted vs. frequency for a Si/SiGe n-MODFET with  $L_g = 80$  nm and  $W_g = 20 \mu m$ . (b) Squares: plot of  $f_T$  and  $f_{max}$  vs.  $V_{ds}$  for same device as in (a) with gate resistance,  $R_g$ , of 2  $\Omega$ . Triangles:  $f_{max}$  vs.  $V_{ds}$  for similar devices with  $R_g = 6 \Omega$ .

Figure 4. De-embedded  $|h_{21}|^2$  and MUG vs. frequency for a Si/SiGe n-MODFET with  $L_g = 70$  nm and  $W_g = 20 \ \mu m$  (circles) and 40  $\mu m$  (squares). The extrapolated  $f_T$  and  $f_{max}$  values are indicated in the legend.

Figure 5. Log-log plot of f<sub>T</sub> vs. V<sub>ds</sub> for a Si/SiGe n-MODFET (solid line) and an SOI Si MOSFET (dashed line).