# **IBM Research Report**

# A Novel Cascode Differential Amplifier

Y. Bruck, G. Burdo, M. Zelikson\*, L. Boreysha

IBM Research Division

Haifa Research Laboratory

Haifa 31905

Israel

\*Intel Scientific Industrial Center M.T.M.

POB 1569

Haifa 31015

Israel

Research Division Almaden - Austin - Beijing - Haifa - India - T. J. Watson - Tokyo - Zurich

### A Novel Cascode Differential Amplifier

<sup>1</sup>Y. BRUCK, *Member IEEE*, <sup>1</sup>G. BURDO, <sup>2</sup>M. ZELIKSON, <sup>1</sup>L. BOREYSHA

<sup>1</sup>High Speed Circuit Department.

IBM Research and Development Laboratories in Haifa.

University of Haifa, Mt. Carmel, 31905, Haifa.

<sup>2</sup>INTEL Scientific Industrial Center. M.T.M. POB 1569, 31015 Haifa

ISRAEL

<yurib@il.ibm.com> <michael.zelikson@intel.com> http://isweb.haifa.ibm.com

Abstract – The Differential Cross-Connected Cascode - a novel cascode circuit - is proposed and investigated. Its fundamental distinction from the Differential Ordinary Cascode consists in the input signal voltage being applied simultaneously to the inputs of common emitter/source and common base/gate stages, and besides the inputs of CE/CS and CB/CG being cross-coupled. We show that the input signal is amplified in the input circuit, furthermore the input impedance and the current gain increase considerably and the bandwidth is essentially expanded. Simulation results of such a cascode designed with IBM BJT transistors are presented. The predicted and actually obtained bandwidths proved to be more than twice as wide as compared with the usual cascode: 8.6 - 18.7 GHz.

Key – Words: -cascode, differential amplifier.

#### 1 Introduction

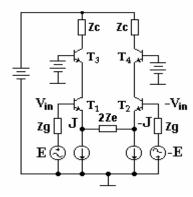

One of the most efficient and frequently used circuits, favoring enhancement of the features of the main amplifying stages is the cascode circuit, i.e. common emitter/source-common base/gate (CE/CS-CB/CG) connections. An uncountable number of papers dealt with its investigation and variants of applications. However, research work continues to appear and new application opportunities are proposed. This is due, first of all, to the features of the functional circuit itself. The simplest variant of this circuit is shown in Fig. 1 in the form of a differential pair.

Further on, we shall call this circuit Differential Ordinary Cascode (for brevity DOC) and for clarity's sake we will consider only its BJT-based type.

A rather full presentation of the properties of the ordinary cascode circuit is given, for instance in [1]. But this simple configuration does not allow increasing cascode current gain, input and output impedances and frequency band of the circuit as compared to the standard CE cell. The main cause is the rigidity of the circuit structure,

which provides feeding of the input signal to the base of the CE stage only.

A great number of inventions and scientific research work has been dedicated to overcoming the drawbacks and limitations of the standard cascode and developing its merits. Let us mention at first the original patent [2], in which proposed in the differential cascode to use input matched resistors cross-coupled between the bases of the CE and emitters of the CB cascades to increase gain and dynamic range. Then denote the work [3], which proposes to apply a negative feedback between the emitter and the base of the CB stage by means of a dedicated amplifier in order to considerably increase the output resistance of the cascode. Finally, the urge towards increase of allowable output voltage, power, efficiency and enhanced matching with the load has lead to the creation of various multistage cascodes [4] and [5] made up of a CE stage and several CB stages.

This brief overview is aimed to show that a signal additionally applied to the base of a CB stage may considerably increase the output

impedance and output voltage of the circuit and somewhat improve the circuit parameters, but does not permit of changing appreciably its transfer function and input resistance. This is quite natural, because the characteristics of the CE stage remain unchanged.

Using regularly the cascode in its differential form, we paid attention to some of its fundamental features, which allow

#### 2 Fundamental

In the framework of this paper we will confine ourselves to the study of a standard (in sense of the implemented functions) differential cascode, i. e. of a circuit in the form of a differential pair intended to convert the input voltage into output current. We will show that feeding in-phase signal current to emitters of the CB stages and simultaneously the anti phase input voltage signal to its bases permits of:

- increasing the current gain;

- expanding the bandwidth of the amplified signals;

- modifying, specifically, diminishing the input admittance.

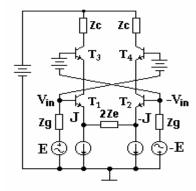

Strictly speaking, such a circuit is no longer a cascode, i. e. a combination of CE-CB stages. Nevertheless, it seems rational to keep this term and, therefore, we call this device hereinafter Differential Cross-Connected Cascode (for brevity - DCC cascode). Its functional circuit is shown in Fig.2 [6].

Let us explain how it works. The transistors  $T_1$ and T<sub>2</sub> are connected in a CE-configuration. Transistors  $T_3$  and  $T_4$  – in a CB-configuration. The transistors  $T_1$  and  $T_3$ , as well as  $T_2$  and  $T_4$ are connected in series to form two cascodes. The bases  $T_1$  and  $T_4$ ,  $T_2$  and  $T_3$  are interconnected and form a DCC cascode. The differential input voltages Vin and -Vin are applied to the bases T<sub>1</sub> and T<sub>2</sub> and generate the currents J and -J, which are injected into the emitters of transistors T<sub>3</sub> и T<sub>4</sub>. The same input voltages are applied to the bases T<sub>4</sub> and T<sub>3</sub>. The base voltages and the base currents of the CB stages are approximately phase (at low opposite by frequency approximation) and are, therefore, perceived by the input voltage sources as negative load impedances.

improving the basic characteristics of the circuit. We will describe the qualitative features of the novel circuit and analyze it theoretically, including comparison with the standard cascode. We also will present a few results of the development of a cascodes with a bandwidth up to 20 GHz.

That is why, the base currents of the CB transistors that are equal to  $Ja_1(1 - a_2)$  are flowing back to the bases of the CE transistors and are subtracted from the CE base currents J (1 -  $a_1$ ). As a result, the total input current of the circuit is decreased to the amount of J (1 -  $2a_1$  +  $a_1a_2$ ) thus decreasing the cascode input current and its input admittance. In our formulas  $a_1$ ,  $a_2$ are the collector-emitter current gain for CE and CB transistors accordingly, and J is the emitter current of the CE stage. A more accurate analysis and simulations with account for the relationship a as a function of frequency and time delay shows that the real part of the input admittance is getting negative and the imaginary (capacitive) part is getting much smaller as frequencies go up. It can be shown that owing to this phenomenon (negative real part of the input admittance); the magnitude of the input voltage at the inputs of the cross-connected circuit grows at frequencies close to the transistor's maximum operating frequency. As a result, the bandwidth of the circuit can be doubled and the total frequency response flatness is improved.

We want to stress that we investigate circuits using n-p-n BJT only for clarity's sake, and all the drawn conclusions are valid for cascodes made of any other amplifying elements.

## 3 Analysis

#### 3.1 The equivalent circuit and restriction

The goal of our theoretical analysis is to investigate the most important phenomenological features of the novel circuit, but in no way to compare in details the theory with the experimental data. That is why; we used the simplest equivalent transistor circuits and, sometimes, even excluded from the cascode circuit some components, which, although

important for its normal functioning, are of minor importance for the analysis of its fundamental features. We used also standard ptype models for the transistors. Formally, these models are suitable for the majority of transistor types. This simple model include: transconductance Gm, input, output and transient conductances Yp, Yo and Yf. The differential form and cross-connection of the cascode were reflected by introducing an ideal input signal phase inverter for the CB stage.

First of all, we will investigate the DCC cascode itself and only afterwards its input circuit. To do this we have to establish beforehand some general rules and restrictions.

- In the frame of this work we consider identical transistor case in CE and CB cascades. General case will consider elsewhere.

- All conductances (resistances) are dimensionless values, normalized on Gm transconductance CE, so Gm = 1. However, for convenience's sake, the parameter Gm is not replaced by 1 when interpreting the formulae. Where it seems desirable, we will use the substitution Z·Gm = T, for instance, Ze·Gm = Te Obviously, T is a certain gain factor. The currents and voltages are also dimensionless values.

- The exact solutions of equation (1) have no great practical importance in most cases, because the transistor model is represented in a simplified way. We assume |Yp|, |Yf|, |Yo| « 1 and |Yf|, |Yo| < |Yp| at all frequencies within the bandwidth of the amplifier and we will, generally, investigate the relationships correct to the terms not higher than second order relatively to these values and/or their cross-referenced terms of the same order.

#### 3.2 Cascodes with identical transistors

Let us consider at first the simplest DCC cascode made up of idealized and identical transistors  $Yp \neq 0$ , Yf = 0, Yo = 0. The exact solutions are given in Eqs.1 and 2.

Now let us discuss these results.

$$Yin = \frac{Yp^2}{\left(Gm + Yp\right)\left[1 + Ze\left(Gm + Yp\right)\right]}$$

(1)

$$Gout = \frac{Gm^2}{\left(Gm + Yp\right)\left[1 + Ze\left(Gm + Yp\right)\right]}$$

(2)

Let us consider now the input current and, therefore, the input conductance of the DCC cascode, which makes its major distinction from the regular DOC. It follows from the circuit and from the relation (1) as well that the input current represents formally the difference of the two base currents of the transistors CE and CB respectively. However, since the current gain of the cascode is a multiplicative process, the cascode input current contains in fact additive multiplicative components and peculiarity is extremely important. The additive components are in opposition and in case of identical transistors canceling each other. This provides wide opportunities in controlling the input impedance. In turn, the multiplicative components allow, for instance, conversing reactive components into active ones. We have to point out that the hereinafter-discussed possibilities to control the frequency dependence of the input conductance in the neighborhood of the bandwidth boundaries are of crucial importance for solving the problem of expanding the DCC cascode bandwidth. We will investigate a few most interesting particular applications of this method.

We assume  $Yp = i \cdot x \cdot Gm$ , where x is a certain relative frequency and  $x \sim 1$  corresponds to a frequency close to the limit one. This, of course, refers to BJT and CMOS transistors as well. Then, proceeding from (1) the relationship of the input conductance dependence  $Y_{DCC}(x)$  from the frequency becomes a very simple one

frequency becomes a very simple one

$$Y_{DCC}(x) = \frac{-Gmx^2}{(1+ix)[1+ZeGm(1+ix)]}$$

(3)

It can be seen from (3) that  $Y_{DCC}(x)$  gets a zero value of the second order at x=0 and two poles on the imaginary axis (at real Ze). At the same time, we can see from (4) that input conductance of the DOC cascode  $Y_{DOC}(x)$  gets only one zero at x=0 and one pole on the imaginary axis.

$$Y_{DOC}(x) = \frac{ixGm}{1 + ZeGm(1 + ix)}$$

(4)

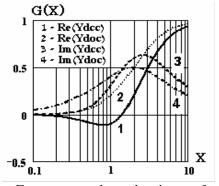

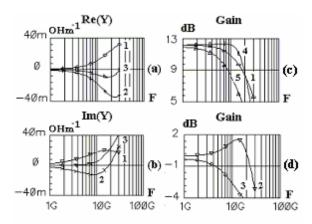

The fundamental distinction between of two cascodes is shown in Fig.3 representing the characteristic dependences of the real component

of the input conductance - curves (1) and (2) - and of its imaginary component - curves (3) and (4) - for both cascode types with the parameter  $Gm_1 = Ze = 1$ .

There are two major distinctions: a considerable reduction of the input conductance and a negative real component of the conductance in the amplifier bandwidth. The last feature is linked to the conversion of the purely imaginary (capacitive) conductance into negative real conductance. The dependence of this real component from the frequency is quadratic at the beginning, but at high frequencies ( $x \approx 1$ ) it depends upon the character and the magnitude of the impedance Ze. Thus, at Im(Ze) = 0 (curve (1) Fig.1), the conductance shows a minimum and is nullified beyond the bandwidth at the point  $Xo = (1+1/Ze\cdot Gm)^{0.5}$ .

Let us emphasize that the transconductance G(x) of both cascodes is described by the single relationship:

$$G(x) = \frac{Gm}{(1+ix)[1+ZeGm(1+ix)]}$$

(5).

#### 3.3 Total transfer function

Total transfer function of the cascode is a product transfer function of cascode itself and transfer function of its input circuit For the same case of identical ideal transistors  $Yp = i \cdot x \cdot Gm$ , Yf = Yo = 0.

$$Y_{21}(x) = \frac{Gm}{1 + ix + Tgx^{2} + Te(1 + ix)^{2}}$$

(6)

Here and hereafter  $Te = Gm \cdot Ze$  and  $Tg = Gm \cdot Zg$ .

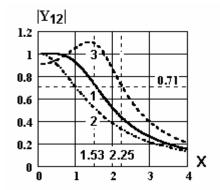

The module  $|Y_{21}|$  is of primary interest. The squared denominator (6) is a polynomial of the  $4^{th}$  order in x. With a predetermined deviation  $|\delta|$  from 1 ( $|\delta| < 1$ ), the optimum transfer function is expressed either by the Butterworth polynomial ( $\delta = 0$ ), or by the Chebyshev polynomial.

Fig.4 shows three transfer functions (6), where (1) and (3) relate to the DCC cascode and function (2) to the regular cascode. The frequency axis x of the function (14) is normalized in such a way, that at x = 1 the gain drop of the regular cascode be equal to -3 dB. Then (1) – the Butterworth characteristic shows 1.53 times more bandwidth and (3) – the

Chebyshev characteristic- 2.25 times more bandwidth at  $|\delta| = 0.1$ .

The cause of such an important broadening of the bandwidth at the same transfer function of the cascode itself (5) is evident. At the input of the regular cascode the signal is attenuated owing to the effect of the input capacitive conductance of the CE stage and, on the contrary, the signal is amplified at the input of the DCC cascode at high frequencies owing to the effect of the negative real component of the input conductance (3).

#### 4 Simulation

We have designed and tested several modifications of the cascode circuit using BJT and FET transistors. The work was aimed to verify the increase of the input impedance, current gain and bandwidth expansion of the DCC cascode predicted by the approximation theory as compared to the DOC cascode.

In the framework of this study we intended to minimize the side effects and the influence of secondary factors affecting the investigation results and the circuit comparison, and also to simplify as far as possible the description of the actually used circuits. In this connection simulation has been limited to the most simple cascode circuits Figs.1 and 2. The dc voltage and current sources are ideal ones. The currents, the voltages and all the components of both the investigated circuits and the transistors themselves are identical and shown in Tables 1 (see below). The main parameters of DCC and DOC cascodes are given in the same table.

Table 1.

|     | T <sub>1</sub> T <sub>4</sub> | Zg Ω  | Ze Ω | Ζc Ω  |      |

|-----|-------------------------------|-------|------|-------|------|

| DCC | 16x0.5                        | 25    | 1.6  | 41    |      |

| DOC | 16x0.5                        | 25    | 1.6  | 41    |      |

|     | Io mA                         | Vcc V | ß dB | Go dB | BW G |

| DCC | 4.2                           | 5.1   | 75   | 12.2  | 18.7 |

| DOC | 4.2                           | 5.1   | 38   | 12.0  | 8.6  |

We describe and briefly discuss the simulation results obtained using the SPECTRE CADENCE simulator. Fig. 10 (see below) shows in detail the data regarding the BJT-based cascode. The curves represented on the respective figure are marked in the text by type-"(3)".

#### **4.1 Input conductance**

Fig.5 shows the dependence from frequency of the real (a) and imaginary (b) components of the transistor input conductances CE (1) and CB (2) and also their sum (3) – that is, the input conductance of the DCC cascode. In full concordance with the analysis given before CB (2) transistor conductance is negative resulting in a dramatic reduction of both the components of the cascode input conductance. If the transistors are identical, the real component of the input conductance is always negative within the bandwidth, since the delay causes the capacitive component to convert into negative active component.

#### 4.2 Frequency response

The various Gain transfer functions of the cascodes - the main characteristics of any amplifier – are given in Figs.5c,d. As repeatedly pointed out before, the voltage transfer function of the cascode itself (1) is identical for both the circuits. Its bandwidth makes 17.1 GHz. The voltage transfer functions of the input circuits DCC (2) and DOC (3) cascodes have bandwidth of 29.5 GHz and 11.5 GHz respectively, in full compliance with the formerly carried out analysis (see, e. g. Fig. 6b). The first one shows a maximum of 1.6 dB at the frequency of 12.9 GHz. As a result, the voltage transfer functions of the DCC (4) and DOC (5) cascodes have a bandwidth of 18.7 GHz and 8.6 GHz respectively.

#### 4.3 Current gain

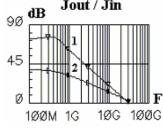

The current gain  $\beta$  of both cascodes is shown in Fig.6. It is evident that  $\beta_{DCC}$  is high and amounts to  $\beta_{DCC} \cong \beta_{DOC}^2$  ( $\beta_{DOC}$  - (2)) up to ~1 GHz. Further,  $\beta_{DCC} < \beta_{DOC}^2$  and this inequality builds up with frequency.

Obviously this is connected with the effect of the output and transient collector-base impedances, which differ in each of the cascodes.

#### 4.4 Noise.

The magnitude and the frequency dependence of the noise factor for DCC and DOC cascades coincide and somewhat exceeds the reference data of a single transistor.

#### 5 Conclusion

The frequency dependences of the input impedances and transfer functions inherent to these circuits have proven to coincide and the approximately twofold bandwidth expansion and the considerable increase of the current gain and input impedance predicted by the theory have been confirmed.

Owing to these features the DCC cascode provides essentially better parameters as compared to the regular cascode in all circuits implemented in our development work using BJT and CMOS transistors.

#### References:

- [1] P. R. Gray, P. J. Hurst, S. H. Lewis and R. G. Meyer. "Analysis and Design of Analog Integrated Circuits." New York; Willey, 2001.

- [2] David A. Moore. "A Low-noise wideband RF differential cascode amplifier with matched input impedance". GB Patent 2356307, May 16, 2001.

- [3] E.Sackinger and W.Guggenbuhl "A High-Swing, High-Impedance MOS Cascode Circuit". *IEEE Journal of Solid-State Circu*it, vol. .25 No 1, pp. 289-298, Feb. 1990.

- [4] Walter E. Milberger, Charles S. Kerfoot, Daniel C. Buck and Franklin B. Jones. "Multistage Cascode Radio Frequency Amplifier." U.S. Patent 5032799, Nov. 26, 1990.

- [5] Mark Rodwell, Shrinivasan Jaganathan and Scott T. Allen. "Series-Connected Microwave Power Amplifiers with Voltage Feedback and Method of Operation for the Same." U.S. Patent 5945879, Feb. 5, 1998.

- [6] Patent pending.

Fig. 1 DOC – Differential Ordinary Cascode schematic.

Fig.2 DCC - Differential cross-connected cascode schematic.

Fig.3. Frequency dependencies of input conductance DOC and DCC cascodes.

Fig.4. Frequency transfer functions of DOC and DCC cascodes: 1 Butterworth characteristic of DCC cascode (T=1, Tg=1.25), 2 Butterworth characteristic of DOC cascode (Te=1, Tg=1.25), 3 Chebyshev characteristic of DCC cascode (Te=1, Tg=4.29,  $\delta$ =0.1).

Fig.5 BJT-based DCC and DOC cascodes. Simulation results (see description in the text).

Fig.6 Current gain DCC (1) and DOC (2) cascades