# **IBM Research Report**

## ForestaPC (Scalable-VLIW) User Instruction Set Architecture

Jaime H. Moreno jmoreno@watson.ibm.com

Kemal Ebcioglu kemal@watson.ibm.com

Mayan Moudgill mayan@watson.ibm.com

IBM T.J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598

Dave Luick luick@rchvmx.vnet.ibm.com

IBM AS/400 Division 3605 Highway 52 N Rochester, MN 55901

#### LIMITED DISTRIBUTION NOTICE

This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g., payment of royalties).

Research Division Almaden • Austin • China • Haifa • Tokyo • T.J. Watson • Zurich

# ForestaPC (Scalable-VLIW) User Instruction Set Architecture

## **Book I**

Version 1.0

December 27, 1996

Copyright International Business Machines Corporation, 1996. All rights reserved

## Preface

This document defines the ForestaPC User Instruction Set Architecture. It covers the base instruction set and related facilities available to the application programmer.

Other related documents are:

- Book II, ForestaPC Virtual Environment Architecture, which defines the storage model and related instructions and facilities available to the application programmer;

- Book III, ForestaPC Operating Environment Architecture, which defines the system (privileged) instructions and related facilities; and

- Book IV, ForestaPC Implementation Features, which defines the implementation-dependent aspects of a particular implementation.

As used in this document, the term "ForestaPC Architecture" refers to the instructions and facilities described in *Books I, II,* and *III.* The description of an instance of the ForestaPC Architecture in a given implementation also includes the material in *Book IV* for that implementation.

# **Table of Contents**

## Chapter 1. Introduction and Formats

| 1.1    | Processor Overview1                          |

|--------|----------------------------------------------|

| 1.1.1  | Basic Description 1                          |

| 1.1.2  | Basic Processor Organization4                |

| 1.1.3  | Semantics of a VLIW5                         |

| 1.1.4  | Speculative Execution                        |

| 1.1.5  | Out-of-order Load Instructions7              |

| 1.2    | Compatibility with the PowerPC Architecture7 |

| 1.3    | Instruction Mnemonics and Operands8          |

| 1.4    | Document Conventions9                        |

| 1.4.1  | Definitions and Notation9                    |

| 1.4.2  | Reserved Fields10                            |

| 1.4.3  | Description of Instruction Operation11       |

| 1.5    | Format of Tree-Instructions12                |

| 1.6    | Formats of Primitive Instructions 13         |

| 1.6.1  | I0-Form                                      |

| 1.6.2  | M0-Form 14                                   |

| 1.6.3  | M1-Form 14                                   |

| 1.6.4  | I1-Form 14                                   |

| 1.6.5  | B2-Form                                      |

| 1.6.6  | D4-Form 14                                   |

| 1.6.7  | X4-Form                                      |

| 1.6.8  | D5-Form                                      |

| 1.6.9  | X6-Form                                      |

| 1.6.10 | D8-Form14                                    |

| 1.6.11 | 18-Form                                      |

| 1.6.12 | X8-Form14                                    |

| 1.6.13 | B10-Form14                                   |

| 1.6.14 | I10-Form 14                                  |

| 1.6.15 | D10-Form                                     |

| 1.6.16 | X10-Form                                     |

| 1.7    | Instruction Fields 15                        |

| 1.8    | Classes of Instructions17                    |

| 1.8.1  | Defined Instruction Class17                  |

| 1.8.2  | Illegal Instruction Class17                  |

| 1.8.3  | Reserved Instruction Class17                 |

| 1.9    | Invalid Instruction Forms17                  |

| 1.10   | Optional Instructions18                      |

| 1.11   | Exceptions                                   |

| 1.12   | Delayed Exceptions                           |

| 1.13   | Storage Addressing 19                        |

| 1.13.1 | Storage Operands                             |

|        | 0 · · · · · · · · · · · · · · · · · · ·      |

## 1.13.2 Effective Address Calculation ......20

# Chapter 2. Registers in the ForestaPC Architecture

| 2.1 General Purpose Registers                     | <u> </u> |

|---------------------------------------------------|----------|

| 2.2 Floating-Point Registers                      | 21       |

| 2.3 Special Purpose Registers                     | 21       |

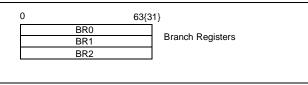

| 2.3.1 Branch Registers                            | 21       |

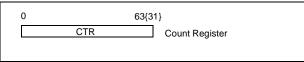

| 2.3.2 Count Register                              | 22       |

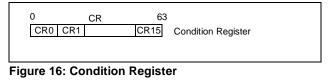

| 2.3.3 Condition Register                          | 22       |

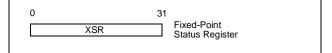

| 2.3.4 Fixed-Point Status Register                 | 23       |

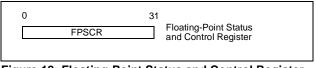

| 2.3.5 Floating-Point Status and Control Register2 | 24       |

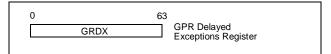

| 2.3.6 GPR Delayed Exceptions Register             | 29       |

| 2.3.7 FPR Delayed Exceptions Register             | 29       |

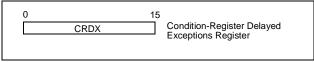

| 2.3.8 CR Delayed Exceptions Register              | 30       |

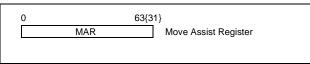

| 2.3.9 Move Assist Register                        | 30       |

## Chapter 3. Branch Instructions

| 3.1   | Fetching Tree-Instructions    | 31 |

|-------|-------------------------------|----|

| 3.2   | Branch Instructions Registers | 32 |

| 3.3   | Multiway Branch Facilities    | 32 |

| 3.4   | Procedure calls               | 33 |

| 3.5   | Branch Primitive Instructions | 33 |

| 3.5.1 | Skip Instruction              | 34 |

| 3.5.2 | Branch Instructions           | 34 |

| 3.5.3 | System Call Instruction       | 35 |

## Chapter 4. Storage Access Instructions

| 4.1   | Storage Access Registers                      |

|-------|-----------------------------------------------|

| 4.2   | General Features                              |

| 4.2.1 | Effective Address                             |

| 4.2.2 | Floating-Point Storage Accesses               |

| 4.2.3 | Storage Access Exceptions                     |

| 4.2.4 | Speculative Load Instructions                 |

| 4.3   | Fixed-Point Load Instructions                 |

| 4.4   | Fixed-Point Store Instructions41              |

| 4.5   | Floating-Point Load Instructions42            |

| 4.6   | Floating-Point Store Instructions43           |

| 4.7   | Fixed-Point Load and Store with Byte Reversal |

|       | Instructions44                                |

| 4.8   | Load Table of Contents Instructions46         |

| 4.9   | Load and Store String Instructions47          |

|       |                                               |

| 4.10 | Storage Synchronization Instructions    | 50 |

|------|-----------------------------------------|----|

| 4.11 | Conditional Store Extender Instructions | 55 |

| 4.12 | Store Extender Instructions             | 55 |

## Chapter 5. Fixed-Point Instructions

| 5.1    | Registers                                      | 59   |

|--------|------------------------------------------------|------|

| 5.2    | General Features                               | 59   |

| 5.3    | Branch Register Instructions                   | 60   |

| 5.4    | Condition Register Logical Instructions        | 61   |

| 5.5    | Condition Register Field Instructions          | 64   |

| 5.6    | Condition Register Instructions                | 65   |

| 5.7    | Extender Instructions                          | 67   |

| 5.8    | Fixed-Point Arithmetic Instructions            | 72   |

| 5.9    | Fixed-Point Multiply and Divide Instructions . | 75   |

| 5.10   | Fixed-Point Compare Instructions               | 83   |

| 5.11   | Fixed-Point Trap Instructions                  | 85   |

| 5.12   | Fixed-Point Select Instructions                | 88   |

| 5.13   | Fixed-Point Logical Instructions               | 89   |

| 5.14   | Fixed-Point Rotate and Shift Instructions      | 95   |

| 5.14.1 | Fixed-Point Rotate Instructions                | 95   |

| 5.14.2 | Fixed-Point Shift Instructions                 | .100 |

| 5.15   | Fixed-Point Move Assist Instructions           | .104 |

| 5.16   | Fixed-Point Shift and Add Instructions         | .107 |

| 5.17   | Move To/From Special Purpose Registers         |      |

|        | Instructions                                   |      |

| 5.18   | Move To/From FPSCR Instructions                |      |

| 5.19   | Move Register Instructions                     |      |

| 5.20   | Commit Instructions                            | .115 |

|        |                                                |      |

## Chapter 6. Floating-Point Instructions

| 6.1   | Floating-Point Overview           | 117 |

|-------|-----------------------------------|-----|

| 6.2   | Floating-Point Data               | 119 |

| 6.2.1 | Data Format                       | 119 |

| 6.2.2 | Value Representation              | 119 |

| 6.2.3 | Sign of Result                    | 121 |

| 6.2.4 | Normalization and Denormalization | 121 |

| 6.2.5 | Data Handling and Precision       | 122 |

| 6.2.6 | Rounding                          | 122 |

| 6.3   | Floating-Point Exceptions         | 123 |

| 6.3.1 | Invalid Operation Exception       | 126 |

| 6.3.2 | Zero Divide Exception             | 127 |

|       |                                   |     |

| 6.6.5 | Floating-Point Select Instruction                         |

|-------|-----------------------------------------------------------|

| 6.6.4 | Instructions140<br>Floating-Point Compare Instructions143 |

| 6.6.3 | Floating-Point Rounding and Conversion                    |

| 6.6.2 | Floating-Point Arithmetic Instructions134                 |

| 6.6.1 | Floating-Point Move Instructions                          |

| 6.6   | Floating-Point Instructions133                            |

| 6.5   | Speculative Execution of Floating-Point<br>Instructions   |

|       | Instructions                                              |

| 6.4.2 | Execution Model for Multiply-Add Type                     |

| 6.4.1 | Execution Model for IEEE Operations                       |

| 6.4   | Floating-Point Execution Models129                        |

| 6.3.5 | Inexact Exception129                                      |

| 6.3.4 | Underflow Exception128                                    |

| 6.3.3 | Overflow Exception128                                     |

tions

## Appendix B. ForestaPC User Instruction Set Sorted by Opcode

## Appendix C. ForestaPC User Instruction Set Sorted by Mnemonic

## Chapter 1. Introduction and Formats

This chapter gives an overview of the *ForestaPC architecture*, discusses the compatibility among the ForestaPC architecture and the PowerPC architecture, describes the format of the ForestaPC instructions, the classes and format of primitive instructions, the exceptions, and the storage addressing.

## 1.1 Processor Overview

## 1.1.1 Basic Description

The ForestaPC architecture defines the register set, the instruction set, the storage model, and other facilities described in this document. This architecture is tailored for extensive exploitation of *instruction-level parallelism (ILP)* in programs, that is, for executing many basic (primitive) instructions at a time. ForestaPC is a *scalable-VLIW* architecture, which also allows implementations exploiting limited instruction-level parallelism (*superscalar* sequential processors).

Implementations of the ForestaPC architecture contain many functional units which are used simultaneously for the execution of multiple primitive instructions.

The ForestaPC architecture allows the following types of implementations:

64-bit implementations, in which all registers excepting some Special Purpose Registers are 64 bits long, and effective addresses are 64-bits long. All 64-bit implementations have two modes of computation: 64-bit mode and 32-bit mode. This mode controls how the effective address is interpreted and how status bits are set. All instructions provided for 64-bit implementations are available in both modes.  32-bit implementations, in which all registers except the Condition Register and the Floating-Point Registers are 32-bits long, and effective addresses are 32bits long.

The instructions defined in this document are provided in 64-bit and 32-bit implementations unless stated otherwise. Instructions provided only for 64-bit implementations are illegal in 32-bit implementations, and vice-versa.

The ForestaPC architecture has two distinct modes of operation, each with a different user instruction set architecture:

- VLIW Native mode, in which programs in storage have an explicit representation of ILP in the form of *tree-instructions*, as defined in this document.

- **PowerPC mode**, in which programs comply with the definitions in the *PowerPC Architecture*. In this mode, a program in storage contains PowerPC primitive instructions.

See *Book I, PowerPC User Instruction Set Architecture,* for additional information regarding the user instruction set architecture in PowerPC mode.

Unless explicitly stated otherwise, the description given in this document refers to VLIW Native mode.

The base mode (VLIW Native mode or PowerPC mode) in use for an instruction is determined by a bit in the Page Table Entry for the page that contains the instruction. Thus, a base mode change is accomplished by simply branching to a page which contains instructions in the mode other than the one in use at a given time. No synchronization instructions are required. Normally, this branch should occur at a function call boundary, so that programs in both modes comply with standard call conventions. A base mode change also occurs when sequential execution flows to a page with instructions in a different mode, but this would not usually be done.

## **64-bit Implementations**

In 64-bit mode and 32-bit mode of a 64-bit implementation, instructions that set a 64-bit register affect all 64-bits, and the value placed in the register is independent of mode. In both modes, effective address computations use all 64-bits of the relevant registers, and produce a 64-bit result. However, in 32-bit mode, the high-order 32 bits of the computed effective address are ignored when accessing data, and are set to 0 when fetching instructions.

## **32-bit Implementations**

For a 32-bit implementation, all reference to 64-bit mode in this document should be disregarded. The semantics of instructions are as shown in this document for 32-bit mode in a 64-bit implementation, except that in a 32-bit implementation all registers other than the Condition Register and the Floating-Point Registers are 32-bits long. Bit numbers for registers are shown in braces ({}) when they differ from the corresponding numbers for a 64-bit implementation, as described in Section 1.4.1, "Definitions and Notation," on page 9.

## **VLIW Native Mode**

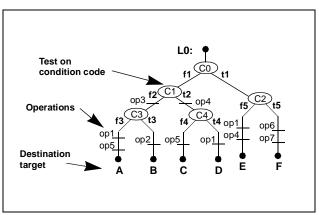

A program executed by a ForestaPC processor in VLIW Native mode consists of a sequence of *tree-instructions* (or simply *trees*), each of which corresponds to an *unlimited multiway-branch* and an *unlimited set of operations* (*primitive instructions*). The multiway-branch is associated with the internal nodes of a tree, whereas the operations are associated with the arcs (see Figure 1). The multiwaybranch is the result of a set of *binary tests on conditions codes*; the left outgoing arc from a tree node corresponds to the false outcome of the test, whereas the right outgoing arc corresponds to the true outcome of the test.

Primitive instructions in a tree are subject to *sequential semantics for each path of the tree,* as if each primitive instruction were executed in the order in which it appears in the tree-path (a tree-path starts from the root of the tree and ends in a destination target). As a result, a primitive instruction cannot use a processor resource which is the target of a previous instruction in the same tree-path. This requirement may not be checked nor enforced by the hardware. If this requirement is not fulfilled within a tree-instruc-

Figure 1: Tree instruction

tion, the results from primitive instructions having an operand set by a previous instruction in the same tree-path are undefined.

Architecture Note: Sequential semantics in each treepath is required to guarantee binary compatibility among different implementations of the ForestaPC architecture, with varying degrees of parallel execution capabilities, so that large trees can be decomposed into subtrees which are executed in different cycles.

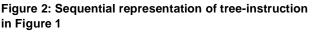

A tree-instruction is represented in main storage as a *contiguous sequence of primitive instructions*, wherein each primitive instruction is encoded in one memory word. The sequence of primitive instructions is obtained from the *depth-first traversal* of the tree-instruction (see Figure 2).

| L0: skip C0,t1     t4: op1       f1: skip C1,t2     b       f2: op3     t1: skip C2,t5 |

|----------------------------------------------------------------------------------------|

| f2: op3 t1: skip C2,t5                                                                 |

|                                                                                        |

|                                                                                        |

| skip C3,t3 f5: opl                                                                     |

| f3: op1 op4                                                                            |

| op5 b E                                                                                |

| b A t5: op6                                                                            |

| t3: op2 op7                                                                            |

| b B b F                                                                                |

| t2: op4                                                                                |

| skip C4,t4                                                                             |

| f4: op5                                                                                |

| b C                                                                                    |

A binary test on a condition code is performed with a *skip* instruction, which corresponds to a flow-control operation within the tree, and which indicates where the tree-path corresponding to the true outcome of the test continues in storage; as a result, a skip instruction is a branch with a (short) positive displacement. All destination targets of the tree are represented as *unconditional branch* instructions, which specify the next tree to be executed when that path of the current tree is selected. Consequently, the end of a tree-instruction is delimited by *an instruction that follows an unconditional branch which is not reachable by any skip instruction within the tree*.

Note that any primitive instruction within a tree-instruction can also correspond to the starting point of another tree. As a result, branching into a tree-instruction leads to the execution of a tree which is a subset of a larger tree.

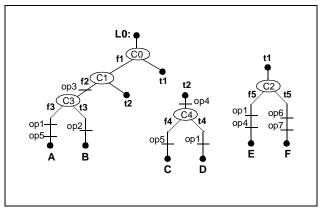

A ForestaPC processor fetches tree-instructions from main storage for execution. If the size of a tree-instruction exceeds the resources in the processor (such as number of branches, number of fixed-point or floating-point operations, and so on), then the tree-instruction is dynamically decomposed (*pruned*) to fit the resources available in the processor (see Figure 3). The resulting subtrees are executed in successive cycles, unless the taken path is completely contained within the first subtree.

Figure 3: Pruning a tree-instruction

**Programming Note:** Better performance after pruning might be obtained by allocating the most frequently taken path to the left-most path in a tree-instruction.

The pruning process transforms arbitrary-size tree-instructions into subtree-instructions which fit the resources available in a processor implementation. These subtrees have the same general structure as the original trees (that is, a multiway-branch tree with operations in the tree-paths), but their size is limited. These subtrees correspond to *Very Long Instruction Words (VLIWs)* which are directly executed by the processor.

The primitive instructions are classified as follows:

- skip and branch instructions;

- storage access instructions;

- fixed-point instructions; and

- floating-point instructions.

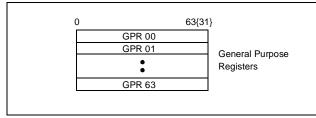

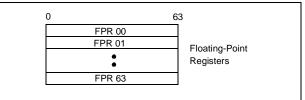

Fixed-point instructions operate on byte, half-word, word, and double-word operands. Floating-point instructions operate on single-precision and double-precision floatingpoint operands. Storage access instructions provide byte, half-word, word, and double-word operand fetches and stores between storage and a set of 64 General Purpose Registers (GPRs). Storage access instructions also provide word and double-word operand fetches and stores between storage and a set of 64 Floating-Point Registers (FPRs).

Signed integers are represented in two's complement form.

No primitive instructions other than store instructions modify storage. To use a storage operand in a computation and then modify the same or another storage location, the contents of storage must be loaded into a register, modified, and then stored back to the target location.

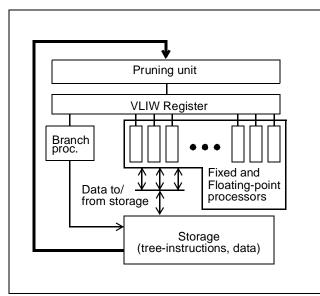

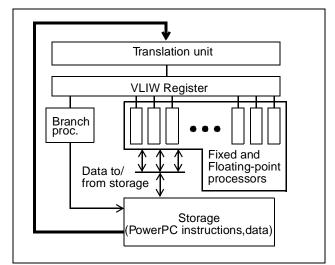

Figure 4 is a logical representation of VLIW Native instruction processing. Tree instructions are fetched from storage and fed into a Pruning Unit, which converts them into VLIWs whose requirements fit the specific implementation. The output from the Pruning Unit is placed in a VLIW Register, which feeds a multiway Branch Processor and multiple Fixed-Point and Floating-Point Processors. The Branch Processor generates the storage address for the next treeinstruction, whereas the Fixed-Point and Floating-Point Processors perform the operations and interact with storage to transfer data.

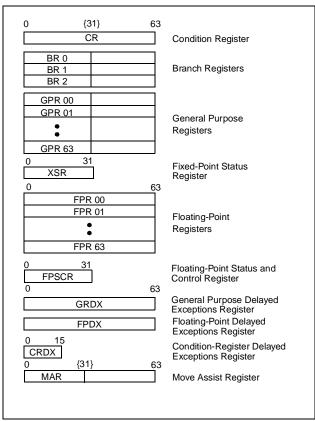

Figure 5 shows the registers available in VLIW Native mode.

Figure 4: Logical processing model in Native mode

Figure 5: Native mode user register set

## PowerPC Mode

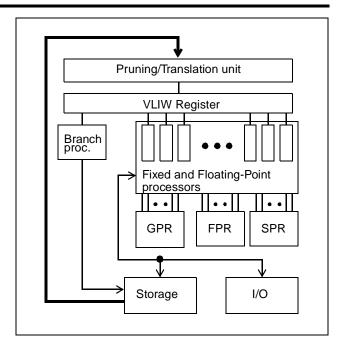

Figure 6 is a logical representation of instruction processing in PowerPC mode. PowerPC primitive instructions are fetched from storage as blocks and fed into the Translation Unit, which converts them into groups of VLIW Native primitive instructions executable in parallel (based on dependencies among the PowerPC instructions and the resources in the processor). The resulting groups can be regarded as single-path tree-instructions. The output from the Translation Unit is placed in the VLIW Register, which feeds the resources in the processor. The Branch Processor generates the storage address for the next PowerPC instruction to be executed after the group, whereas the Fixed-Point and Floating-Point Processors perform the operations and interact with storage to transfer data.

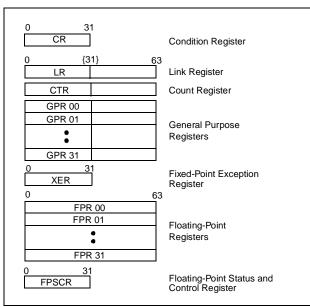

Figure 7 shows the registers available in PowerPC mode (the same ones as in the PowerPC architecture).

Figure 6: Logical processing model in PowerPC mode

The description of the primitive instructions in PowerPC mode is not given in this document; they are defined in *Book I, PowerPC User Instruction Set Architecture.*

## 1.1.2 Basic Processor Organization

The basic components of a ForestaPC processor are as follows (see Figure 8):

- a Pruning/Translation Unit

- a Very Long Instruction Word (VLIW) Register;

- a (multiported) General Purpose Register (GPR) file;

Figure 7: PowerPC mode user register set

- a (multiported) Floating-Point Register (FPR) file;

- a (multiported) set of Special Purpose Registers (SPRs).

- a Multiway-Branch Processor;

- an implementation-dependent number of Fixed-Point Processors;

- an implementation-dependent number of Floating-Point Processors;

- a Storage Subsystem;

- an Input/Output Subsystem.

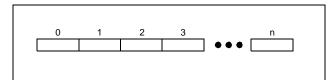

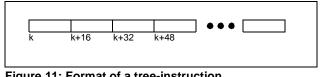

The Very Long Instruction Word register (see Figure 11) is divided into *slots* or *parcels* of one word (32 bits each), which are numbered from left to right (starting from 0). A set of primitive instructions are allocated to the slots in the VLIW register.

Fixed-Point and Floating-Point processors are associated with slots within a VLIW, and are interconnected among themselves in nearest-neighbor fashion; for example, there is a path between the processor in slot k and the processor in slot k-1, between the processor in slot k-1 and the processor in slot k-2, and so on. However, there is no path between the processor in slot 0 (the leftmost slot) and the processor in the righmost slot. The existing paths are used by some special *Extender instructions* which allow creating multiparcel primitive instructions.

Figure 8: ForestaPC processor

Figure 9: Format of Very-Long Instruction Word register

## 1.1.3 Semantics of a VLIW

Very Long Instruction Words specify a multiway-branch (Skip and Branch instructions) and a number of Fixed-Point, Storage Access, and Floating-Point instructions, all executable concurrently. The semantics of this group of instructions is as follows:

Instructions that are on the taken path of the multiwaybranch (as determined by the outcome from the conditions in the *skip* instructions) are executed to completion and their results placed in the corresponding target registers or storage locations.

In contrast, instructions that are not on the taken path of the multiway-branch are inhibited from committing their results to storage or registers. Such instructions do not produce any effect on the state of the processor, nor are they observed by other processors.

- The following rules apply to instructions that are on the taken path of the multiway-branch:

- All instructions are executed concurrently.

- The results from all instructions are subject to sequential semantics. The results from an operation that uses a processor resource set by a previous operation in the path are undefined.

- If two or more instructions target the same memory byte, register, field or bit of certain special registers, the value placed in that target corresponds to the instruction appearing later in the tree-instruction (in sequential storage order).

## 1.1.4 Speculative Execution

Speculative execution is a technique usable by the compiler (programmer) for improving performance in VLIW Native mode.

A *speculative operation* is one that has been placed above a branch with respect to a sequential execution stream, on the *speculation* that the result will be needed. If subsequent events indicate that the speculative instruction would not have been executed, or the results of the speculative instruction are not valid, any result produced by the instruction is not used. Typically, instructions are placed speculatively by the compiler/programmer when there are resources that would otherwise be idle so that the operation is done without cost, or when it might lead to reducing delays in the program.

Most fixed-point instructions (*Arithmetic, Logic, Load* instructions including *Floating-Point Loads*) can be executed speculatively. *Store* instructions should not be executed speculatively, nor should other instructions that produce unrecoverable effects.

An operand which has been loaded or computed speculatively, and any value derived from it, must be *committed* before it can be used non-speculatively (usually, at the original place in the sequential instruction stream). Special instructions are available to commit speculative operands.

No error of any kind other than Machine Check is reported due to the execution of a speculative instruction, until the result from its execution (or any other result derived from it) is committed. If there were errors, the instruction should be re-executed at that point, as well as any other instructions already executed that depend on the speculative operation. Speculative execution is supported by the following resources and procedures:

- Each GPR, FPR and CR Field has an associated *Delayed Exception* bit, which is used to report (in delayed manner) if an exception occurred during execution of a speculative instruction which targets the corresponding register or field.

- Reading a register whose Delayed Exception bit is 1 either raises an exception or propagates the Delayed Exception bit to the target register of the operation, as follows:

- if the operation is a *commit operation*, then a *delayed exception* is raised to the processor;

- if the register is used to generate the address of a memory location accessed by a store operation, then an *invalid operation exception* is raised to the processor;

- otherwise, the Delayed Exception bit associated with each target register of the operation is set to 1; the register contents become undefined.

- Placing in storage a register whose Delayed Exception bit may be set to 1 requires storing the Delayed Exception bit explicitly. Similarly, reading from storage a value which may have associated a Delayed Exception bit set to 1 requires reading the Delayed exception bit explicitly.

- Speculative load operations are identified as such through a Speculative Flag bit SF=1 in the instruction. No other speculative operations are explicitly identified as such.

- Speculative load operations that succeed (i.e., that do not raise an exception) are observed by other processors, as described in Book II, ForestaPC Virtual Environment Architecture. Speculative load operations that do not succeed set the Delayed Exception bit in the target register, and are not observed by other processors.

- An operand which has been generated speculatively is committed by executing a *Commit* instruction. The architecture includes *Commit* instructions for General-Purpose Registers, Floating-Point Registers, and Condition Register Fields. These instructions copy a speculative register contents into another register (of the same type), checking the *Delayed Exception* bit in the process. If the Delayed Exception bit is not set, the move register operation proceeds; otherwise, a *delayed exception* is generated.

- When a delayed exception is raised by a *Commit* instruction, the exception handler activates recovery code which re-executes the speculative instruction which generated the exception as well as those instructions that depend on it and which were executed before the exception was raised. For these purposes, the instructions executed between the speculative instruction generating the exception and the commit operation must not destroy the operands of the instructions that are re-executed in the recovery code.

- Speculation of other operations is managed by the compiler (programmer), without explicit indication.

The Delayed Exception bits of General Purpose Registers, Floating-Point Registers, and 4-bit Condition Register Fields are kept in special purpose registers GRDX, FPDX, and CRDX, respectively. GRDX contains the Delayed Exception bits of General Purpose Registers 0 to 63, in left to right order. FPDX contains the Delayed Exception bits of Floating-Point Registers 0 to 63, also in left to right order. CRDX contains the Delayed Exception bits of CR fields 0 to 15, also in left to right order.

## 1.1.5 Out-of-order Load Instructions

An *out-of-order Load* instruction is one that has been placed above a *Store* instruction with respect to sequential execution. *Load* instructions frequently start a sequence of dependent operations that depend on the datum loaded, so it is advantageous to initiate the loads as early as possible. However, an out-of-order *Load* may conflict with a *Store* operation over which it has been moved if the addresses of the *Load* and *Store* cannot be disambiguated by the compiler (programmer).

A software-based coherence test allows reordering load instructions relative to store instructions, in spite of the possibility of conflicts due to memory references which cannot be disambiguated. Whenever a Load instruction is moved earlier than a sequentially preceding ambiguous Store instruction by the compiler(programmer), a coherence test is inserted at the original position of the Load instruction in the sequential instruction stream. The coherence test consists of two instructions: a Load instruction from the same memory location, followed by a Trap if not equal instruction which compares the value just loaded with the value loaded out-of-order. If the values are identical, then the value loaded out-of-order and all other values derived from it are correct, and execution can proceed normally. On the other hand, if the value just loaded is different from the value loaded out-of-order (which implies that the corresponding memory location has been modified after been read), then the value loaded out-of-order as well as all other values derived from it are incorrect and must be recomputed.

As in the case of speculative instructions that raise exceptions, when a trap is generated by the *Trap if not equal* instruction that is part of the coherence test, the trap handler activates recovery code which re-executes the out-oforder load instruction as well as those instructions that depend on it and which were executed before the trap was generated. For these purposes, the instructions executed between the out-of-order load instruction and the coherence test must not destroy the operands of the instructions that are re-executed in the recovery code.

# 1.2 Compatibility with the PowerPC Architecture

In PowerPC mode, the ForestaPC architecture provides binary compatibility with the PowerPC Architecture; the User Instruction Set Architecture is the same.

In VLIW Native mode, the ForestaPC architecture does not provide binary compatibility for PowerPC programs. Instead, the ForestaPC architecture relies on object-code translation into ForestaPC code; some primitive instructions in the architecture are intended to facilitate objectcode translation.

A summary of the incompatibilities among the PowerPC Architecture and the ForestaPC Architecture in VLIW Native mode is described in this section.

Many of the primitive instructions have the same functionality as PowerPC instructions, though they have different instruction format and opcode encoding. In most of these cases, the ForestaPC instruction name and mnemonics are the same as those in PowerPC. Due to the differences in architecture, some PowerPC instructions do not exist in the ForestaPC architecture; their functionality is achieved by several ForestaPC primitive instructions executed sequentially or in parallel. In addition, some new instructions have been incorporated.

The register set is larger than the one available in the PowerPC architecture; in particular, there are 64 General Purpose Registers, 64 Floating-Point Registers and 16 Condition Register fields, in addition to several new Special Purpose Registers. Some PowerPC Special Purpose Registers are not available, or are set differently. Storage access instructions have a 11-bit signed displacement field; this is in contrast to the PowerPC architecture, wherein most storage access instructions have a 16-bit signed displacement. Moreover, there is a single address mode (register plus displacement); there are no *indexed mode* nor *update form* of storage access instructions, as in the PowerPC architecture.

Primitive instructions do not have the equivalent of the Rc bit available in the PowerPC architecture to set CR0 or CR1. In contrast, primitive instructions that set the Condition Register can directly set any of the sixteen Condition Register fields. Fixed-point instructions that do not have a CR field can be augmented with a special *Extender* instruction specifying a CR field.

XSR is the register corresponding to XER in the PowerPC architecture. However, XSR is set only by special *Move to Special-Purpose Register* instructions. All other fixed-point instructions do not set XSR directly. Instead, all other fixed-point instructions generate a value called *Fixed-Point Status Image (XSR-Image)*. Fixed-point instructions can be augmented with a special *Extender* instruction specifying a General Purpose Register; the *Extender* is used to place the XSR-Image generated by the instruction being augmented into the specified General Purpose Register. This approach is used to enhance instruction-level parallelism by allowing the simultaneous execution of multiple instructions that set fields of XSR (CA, OV).

FPSCR is set only by special *Move to FPSCR* instructions. All other floating-point instructions do not set FPSCR directly. Instead, all other floating-point instructions generate a value called *Floating-Point Status Image (FSR-Image)*. Floating-point instructions can be augmented with a special *Extender* instruction specifying a General Purpose Register; the *Extender* is used to place the FSR-Image generated by the instruction being augmented into the specified General Purpose Register. This approach is used to enhance instruction-level parallelism by allowing the simultaneous execution of multiple instructions that set fields of FPSCR.

Floating-point instructions can be augmented with a special *Extender* instruction which specifies the immediate generation of exceptions arising from the execution of the floating-point operations.

String, load/store multiple, and other complex PowerPC primitives (such as *rlwimi and rldimi*) have been excluded from the architecture; their functionality is implemented by a series of simpler primitive instructions.

# **1.3 Instruction Mnemonics and Operands**

In PowerPC mode, each instruction has the same representation and features defined in *Book I, PowerPC User Instruction Set Architecture.* See that document for additional details; further information is not provided here.

For VLIW Native mode, the description of each primitive instruction includes the mnemonics and a formatted list of operands. Some examples are

- stw RS,D(RA)

- addi RT,RA,SI

- Idbz? RT,D(RA)

In most cases, the mnemonics are the same ones as in the PowerPC architecture. A load instruction mnemonic ending with the symbol "?" indicates that the instruction is *specula-tive*.

The description of every tree-instruction starts with a label, and includes the specification of *skips, branches*, and other primitive instructions. *Skip* and *branch* instructions have an associated label. An example of tree-instruction is depicted in Figure 10.

| L0: s<br>f1: s | -    | cr0.ne,t1        |

|----------------|------|------------------|

| f1: s          |      |                  |

|                | skip | crl.gt,t2        |

| f2: a          | add  | r10,cr8,r14,r56  |

| S              | skip | cr3.eq,t3        |

| f3: s          | subf | r12,cr9,r14,r44  |

| a              | andi | r22,r16,0x34     |

| k              | D    | A                |

| t3: c          | or   | r16,cr10,r16,r17 |

| k              | D C  | В                |

| t2: a          | addi | r21,r16,0x1234   |

| S              | skip | cr4.lt,t4        |

| f4: a          | andi | r22,r16,0x34     |

| k              | D C  | C                |

| t4: s          | subf | r12,cr9,r14,r44  |

| k              | D C  | D                |

| t1: s          | skip | cr2.eq,t5        |

| f5: s          | subf | r12,cr9,r14,r44  |

| ā              | addi | r21,r16,0x1234   |

| k              | C    | E                |

| t5: 1          | Lbz  | r23,64(r2)       |

| S              | stw  | r24,32(r2)       |

| k              | D    | F                |

Figure 10: Example of a tree-instruction

ForestaPC-compliant assemblers will support the mnemonics and operand lists exactly as shown, and will also provide certain extended mnemonics. They may also provide high-level representations for multiway-branches, such as nested if-then-else and goto constructs.

## **1.4 Document Conventions**

## 1.4.1 Definitions and Notation

The following definitions and notation are used throughout the ForestaPC Architecture documents.

- A VLIW Native program is a sequence of related treeinstructions.

- A PowerPC program is a sequence of related PowerPC instructions.

- A tree-instruction is a variable-length sequence of primitive instructions; each primitive instruction is one word long (32 bits per word).

- A tree-path is a path within a tree-instruction starting at the first operation in the tree and ending in an unconditional branch instruction.

- A tree-branch is a subtree starting at the target of a skip instruction.

- The binary tests in a tree-instruction comprise a multiway-branch which, at run time, selects one out of several tree-paths; the selected path is also called the taken path. Only those operations on the selected tree-path are actually executed.

- VLIW refers to a Very Long Instruction Word whose length is implementation-dependent. A VLIW corresponds to a tree-instruction not exceeding the resources of the implementation.

- Primitive instruction (or just instruction) refers to a 32bit *native* or *primitive* instruction word.

- Slot or parcel refers to a 32-bit word within a VLIW, which contains a primitive instruction. Slots are numbered from left to right, starting from slot 0.

- Quadwords are 128 bits, doublewords are 64 bits, words are 32 bits, halfwords are 16 bits, and bytes are 8 bits.

- All numbers are decimal unless specified in some special way.

- Obnnnn means a number expressed in binary format.

- Oxnnnn means a number expressed in hexadecimal format.

- Underscores may be used between digits.

- The symbol || is used to describe the concatenation of two values. For example, 010 || 111 is the same as 010111.

- RT, RA, RB, ... refer to General Purpose Registers.

- FRT, FRA, FRB, ... refer to Floating-Point Registers.

- BRT, BRS refer to Branch Registers.

- (x) means the contents of register x, wherein x is the name of an instruction field. For example, (RA) means the contents of register RA, and (FRA) means the contents of register FRA, wherein RA and FRA are instruction fields. Names such as BR0 and XSR denote registers, not fields, so parentheses are not used with them. In addition, when register x is assigned a value, parentheses are omitted.

- (RA|0) means the contents of register RA if the RA field has the value 1-63, or the value 0 if the RA field is 0.

- Bits in registers, instructions, storage and fields are specified as follows.

- Bits are numbered left to right, starting with bit 0.

- Ranges of bits are specified by two numbers separated by a colon (:). For example, the range 3:8 consists of bits 3 through 8.

- For registers that are 64-bits long in 64-bit implementations and 32-bits long in 32-bit implementations, bit numbers and ranges are specified with the values for 32-bit implementations enclosed in braces ({}). {} means a bit that does not exist in 32-bit implementations. {:} means a range that does not exist in 32-bit implementations.

- $X_p$  means bit p of register/field X.  $X_{p\{r\}}$  means bit p of register/field X in a 64-bit implementation, and bit r of register/field X in a 32-bit implementation.

- X<sub>p:q</sub> means bits p through q of register/field X.

X<sub>p:q{r:s}</sub> means bits p through q of register/field X in a 64-bit implementation, and bits r through s of register/field X in a 32-bit implementation.

- X<sub>p q ...</sub> means bits p, q, ... of register/field X.

X<sub>p q ...</sub> {r s ...} means bits p, q, ... of register/field X in a 64-bit implementation, and bits r, s, ... of register/field X in a 32-bit implementation.

- ¬(RA) means the one's complement of the contents of register RA.

- 2<sup>n</sup> means 2 raised to the n<sup>th</sup> power.

- <sup>n</sup>x means the replication of x, n times (i.e., x concatenated to itself n-1 times). <sup>n</sup>O and <sup>n</sup>1 are particular cases:

- <sup>n</sup>0 means a field of n bits with each bit equal to 0. Thus, <sup>5</sup>0 is equivalent to 0b00000.

- <sup>n</sup>1 means a field of n bits with each bit equal to 1. Thus, <sup>5</sup>1 is equivalent to 0b11111.

- Positive means greater than zero.

- Negative means less than zero.

- A speculative instruction is an instruction that has been moved above a sequentially preceding conditional branch.

- An out-of-order *Load* instruction is an instruction that has been moved above a sequentially preceding *Store* instruction.

- A *Load* instruction mnemonics followed by the symbol "?" indicates a speculative load instruction.

- A system library program is a component of the system software that can be invoked by an application program using a *Branch* instruction.

- A system service program is a component of the system software that can be invoked by an application program using a *System Call* instruction.

- The system trap handler is a component of the system software that receives control when the conditions specified in a *Trap* instruction are satisfied.

- The system error handler is a component of the system software that receives control when an error occurs. The system error handler includes a component for each of the various kinds of errors. These error-specific components are referred to as the system alignment error handler, the system data storage error handler, etc.

- Each bit and field in instructions, in status and control registers (XSR and FPSCR), and in Special Purpose Registers, is either defined or reserved.

- /, //, ///, ... denotes a reserved field in an instruction or in an architected storage table.

- Latency refers to the interval from the time an instruction begins execution until it produces a result that is available for use by a subsequent instruction.

- Unavailable refers to a resource that cannot be used by the program. Data or instruction storage is unavailable if an instruction is denied access to it. See Book III, ForestaPC Operating Environment Architecture.

- The results of executing a given instruction are said to be boundedly undefined if they could have been achieved by executing an arbitrary sequence of instructions, starting in the state the machine was in before executing the given instruction. Boundedly undefined results for a given instruction may vary among implementations, and among different executions on the same implementation, and are not further defined in this document.

- The sequential execution model in VLIW Native mode is the model of program execution described in Section 3.1, "Fetching Tree-Instructions," on page 31.

## 1.4.2 Reserved Fields

All reserved fields in primitive instructions should be zero. If they are not, the instruction form is invalid (see Section 1.9, "Invalid Instruction Forms," on page 17).

The handling of reserved bits in status and control registers, and in Special Purpose Registers, is implementationdependent. For each such reserved bit, an implementation shall either:

- ignore the source value for the bit on write, and return zero for it on read; or

- set the bit from the source on write, and return the value last set for it on read.

- **Programming Note:** It is the responsibility of software to preserve bits that are now reserved in status and control registers and in Special Purpose Registers, as they may be assigned a meaning in some future version of the architecture. In order to accomplish this preservation in implementation independent manner, software should do the following:

- Initialize each such register supplying zeroes for all reserved bits.

- Alter (defined) bit(s) in the register by reading the register, altering only the desired bit(s), and then writing the new value back to the register.

XSR and FPSCR are partial exceptions to this recommendation. Software can alter the status bits in these registers, preserving the reserved bits, by executing instructions that have the side effect of altering the status bits. Similarly, software can alter any defined bit in the FPSCR by executing a *Floating-Point Status and Control Register*

instruction. Using such instructions is likely to yield better performance than using the method described in the second item above.

When a currently reserved bit is subsequently assigned a meaning, every effort will be made to have the value to which the system initializes the bit correspond to the "old behavior".

# **1.4.3 Description of Instruction Operation**

The operation of all primitive instructions is described textually. In addition, the operation of most primitive instructions is described by a semiformal language at the register transfer level (RTL). This RTL uses the notation summarized below, in addition to the definitions and notation described in Section 1.4.1, "Definitions and Notation," on page 9. RTL notation not summarized here should be selfexplanatory.

The RTL descriptions cover the normal execution of the instructions, except that *standard* setting of the Condition Register is not shown. (*Non-standard* setting of this registers, such as the setting of Condition Register Field 8 by the *stwc* instruction, is shown.) Fields of the XSR-Image or FSR-Image generated by an instruction are indicated. The RTL descriptions do not cover cases in which the system error handler is invoked, or for which the results are boundedly undefined.

The RTL descriptions specify the architectural transformation performed by the execution of an instruction. They do not imply any particular implementation.

The following elements are used in the RTL descriptions:

| Notation         | Meaning                                                                                                                                              | MASK(x             |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| $\leftarrow$     | Assignment                                                                                                                                           |                    |  |

| ← <sub>iea</sub> | Assignment of an instruction effective address. In 32-bit mode of a 64-bit implementation, the high-order 32-bits of the 64-bit target are set to 0. | MEM(x,y            |  |

| -                | NOT logical operator                                                                                                                                 | DOTI               |  |

| +                | Two's complement addition                                                                                                                            | ROTL <sub>64</sub> |  |

| -                | Two's complement subtraction, unary minus                                                                                                            | ROTL <sub>32</sub> |  |

| ×                | Multiplication                                                                                                                                       |                    |  |

| Notation                        | Meaning                                                                                                                                                                                                                                       |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ÷                               | Division (yielding quotient)                                                                                                                                                                                                                  |

| $\checkmark$                    | Square root                                                                                                                                                                                                                                   |

| =, ≠                            | Equals and Not Equals relations                                                                                                                                                                                                               |

| $<,\leq,>,\geq$                 | Signed comparison relations                                                                                                                                                                                                                   |

| < <sup>u</sup> , > <sup>u</sup> | Unsigned comparison relations                                                                                                                                                                                                                 |

| ?                               | When used as a relation, unordered comparison relation; when used as a value, an implementation-dependent 0/1 (false/true) 1-bit value with implementation-dependent variability; when used in an instruction mnemonic, speculative operation |

| &,                              | AND, OR logical operators                                                                                                                                                                                                                     |

| ⊕,≡                             | Exclusive-OR, Equivalence logical<br>operators ((a≡b) = (a⊕¬b))                                                                                                                                                                               |

| ABS(x)                          | Absolute value of x                                                                                                                                                                                                                           |

| BR0, BR1, BR2                   | Branch Registers                                                                                                                                                                                                                              |

| CEIL(x)                         | Least integer $\ge x$                                                                                                                                                                                                                         |

| CRB                             | Condition Register viewed as 64 independently-addressable bits                                                                                                                                                                                |

| DOUBLE(x)                       | Result of converting x from floating-<br>point single format to floating-point<br>double format, using the model given<br>in page 42                                                                                                          |

| EXTS(s)                         | Result of extending x on the left with sign bits                                                                                                                                                                                              |

| FLOOR(x)                        | Greatest integer $\leq x$                                                                                                                                                                                                                     |

| FPR(x)                          | Floating-Point Register x                                                                                                                                                                                                                     |

| GPR(x)                          | General Purpose Register x                                                                                                                                                                                                                    |

| MASK(x,y)                       | Mask having 1's in positions x<br>through y (wrapping if x > y) and 0's<br>elsewhere                                                                                                                                                          |

| MEM(x,y)                        | Contents of y bytes of memory start-<br>ing at address x. In 32-bit mode of a<br>64-bit implementation, the high-<br>order 32-bits of the 64-bit value are<br>ignored.                                                                        |

| ROTL <sub>64</sub> (x,y)        | Result of rotating the 64-bit value x left by y positions.                                                                                                                                                                                    |

| ROTL <sub>32</sub> (x,y)        | Result of rotating the 64-bit value x  x<br>left by y positions, where x is 32 bits<br>long                                                                                                                                                   |

#### Meaning

Notation

- SINGLE(X)Result of converting x from floating-point<br/>double format to floating-point<br/>single format, using the model shown<br/>on page 42SPREG(x)Special Purpose Register x

- TRAP Invoke the system trap handler

- characterization Reference to the setting of status bits, in a standard way that is explained in the text

- undefined An undefined value. The value may vary among implementations, and among different executions on the same implementation

- CIA Current Instruction Address, which is the 64{32}-bit address of the primitive instruction being described by a sequence of RTL. In 32-bit mode of a 64-bit implementation, the highorder 32-bits of CIA are always set to 0. Does not correspond to any architected register.

- NIA Next Instruction Address, which is the 64{32}-bit address of the next primitive instruction to be executed. In 32-bit mode of a 64-bit implementation, the high-order 32-bits of NIA are always set to 0. Does not correspond to any architected register.

- XSR-Image XSR-Image generated by an instruction. The bit-definitions of this image are the same as those in the XSR register, excepting the Summary Overflow bit which is not defined. Does not correspond to any architected register.

- FSR-Image FSR-Image generated by a floatingpoint instruction. The bit-definitions of this image are the same as the status bits in the FPSCR register, excepting the Summary bits which are not defined. Does not correspond to any architected register.

- if ... then ... else Conditional execution, indenting shows range, else is optional

- do Do loop, indenting shows range. "To" and/or "by" clauses specify incrementing an iteration variable, and a "while" clause gives termination conditions leave Leave innermost do loop, or do loop

- Ave Leave innermost do loop, or do loop described in leave statement

## 1.4.3.1 Precedence Rules

The precedence rules for RTL operators are summarized in Table 1. Operators at higher rows in the table are applied before those at lower rows. Operators at the same row in the table associate from left to right, from right to left, or not at all, as indicated in each case. For example, - associates from left to right, so a-b-c=(a-b)-c. Parentheses are used to override the evaluation order implied by the table, or to increase clarity; parenthesized expressions are evaluated before serving as operands.

#### TABLE 1. Operator Precedence

| Operators                                                            | Associativity |

|----------------------------------------------------------------------|---------------|

| subscript, function evaluation                                       | left to right |

| pre-superscript (replication), post-<br>superscript (exponentiation) | right to left |

| unary -, ¬                                                           | right to left |

| ×, ÷                                                                 | left to right |

| +, -                                                                 | left to right |

|                                                                      | left to right |

| $=,\neq,<,\leq,>,\geq,<^{U},>^{U}$                                   | left to right |

| &, ⊕, ≡                                                              | left to right |

|                                                                      | left to right |

| : (range)                                                            | none          |

| $\leftarrow$ (assignment)                                            | none          |

## 1.5 Format of Tree-Instructions

All tree-instructions are aligned on a word (4-byte) boundary. Whenever tree-instruction addresses are presented to the processor, the two least-significant bits are ignored. Similarly, whenever the processor produces a tree-instruction address, the two least-significant bits are zero.

The format of a tree-instruction consists of a sequence of contiguous words (four bytes), as illustrated in Figure 11.

Figure 11: Format of a tree-instruction

**12 Format of Tree-Instructions**

## **1.6 Formats of Primitive Instructions**

All primitive instructions are one word (four bytes) long and word aligned.

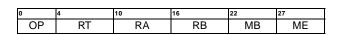

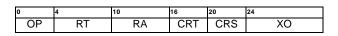

Bits 0:3 of a primitive instruction always specify the primitive opcode (OP). Most primitive instructions also have an extended opcode (XO). The remaining bits of the primitive instruction contain one or more fields, as shown below for the different instruction formats. In all cases, the value of field OP determines the length of field XO.

**Editor's Note:** The assignment of opcodes to instructions (enumeration of the instructions assigned to each primary and extended opcode) is tentative. The assignment might be revised in a future version of the architecture.

The format diagrams given below show horizontally all valid combinations of instruction fields. The diagrams include instruction fields that are used only by instructions defined in *Book II, ForestaPC Virtual Environment Architecture*, or *Book III, ForestaPC Operating Environment Architecture*. See those Books for the definition of such fields. The name of a format ends with a number which specifies the length of the extended opcode field.

In some cases an instruction field is reserved, or must contain a particular value. If a reserved field does not have all bits set to 0, or if a field that must contain a particular value does not contain that value, the instruction form is invalid and the results are as described in Section 1.9, "Invalid Instruction Forms," on page 17.

#### **Split Field Notation.**

In some cases an instruction field occupies more than one contiguous sequence of bits, or occupies one contiguous sequence of bits which are used in permuted order. Such a field is called a *split field*. In the format diagrams given below and in the individual instruction layouts, the name of a split field is shown in lowercase characters, once for each of the contiguous sequences, followed by an identification digit. In the RTL description of an instruction having a split field, the name of the split field in uppercase characters represents the concatenation of the sequences from left to right in increasing order of identification digit. In all other cases, and in certain places where individual bits of a split field are identified, the name of the field in lowercase characters represents the concatenation of the sequences in a split field are identified, the name of the field in lowercase characters represents the concatenation of the sequences in a split field are identified, the name of the field in lowercase characters represents the concatenation of the sequences in a split field are identified.

some order, which need not be left to right, as described for each relevant instruction

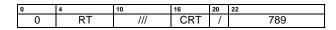

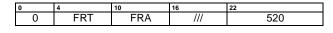

## 1.6.1 IO-Form

| 0  | 4  | 10 | 16 |

|----|----|----|----|

| OP | RT | RA | SI |

| OP | RT | RA | UI |

## 1.6.2 M0-Form

## 1.6.3 M1-Form

| 0  | 4  | 10 | 16              | 17 | 22 | 27              | 31 |

|----|----|----|-----------------|----|----|-----------------|----|

| OP | RT | RA | me <sub>1</sub> | SH | MB | $\mathrm{me}_0$ | хо |

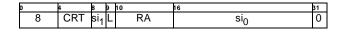

## 1.6.4 **I1-Form**

| 0  | 4   | 8               | 9 | 10 | 16              | 31 |

|----|-----|-----------------|---|----|-----------------|----|

| OP | CRT | si <sub>1</sub> | L | RA | si <sub>0</sub> | хо |

| OP | CRT | ui <sub>1</sub> | L | RA | ui <sub>0</sub> | ХО |

## 1.6.5 B2-Form

| 0  | 4   | 6    | 30 |

|----|-----|------|----|

| OP |     | ADDR | XO |

| OP | BRT | ADDR | ХО |

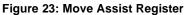

## 1.6.6 D4-Form

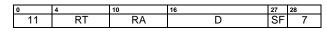

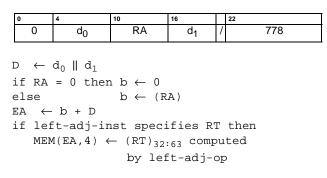

| 0  | 4   | 10              | 16              | 27 | 28 |

|----|-----|-----------------|-----------------|----|----|

| OP | RT  | RA              | D               | SF | XO |

| OP | RT  | dl <sub>1</sub> | dl <sub>0</sub> | SF | хо |

| OP | FRT | RA              | D               | SF | XO |

## 1.6.7 X4-Form

| 0  | 4   | 10  | 16  | 22  | 28 |

|----|-----|-----|-----|-----|----|

| OP | FRT | FRA | FRB | FRC | XO |

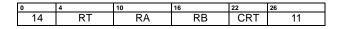

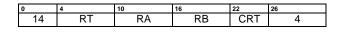

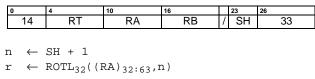

| OP | RT  | RA  | RB  | MB  | XO |

| OP | RT  | RA  | RB  | ME  | XO |

| OP | RT  | RA  | SH  | MB  | XO |

| OP | RT  | RA  | SH  | ME  | XO |

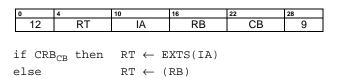

| OP | RT  | IA  | IB  | СВ  | XO |

| OP | RT  | IA  | RB  | СВ  | XO |

| OP | RT  | RA  | IB  | CB  | XO |

| OP | RT  | RA  | RB  | CB  | XO |

### **14 Formats of Primitive Instructions**

## 1.6.8 D5-Form

| 0  | 4              | 10 | 16  | 22             | 27 |

|----|----------------|----|-----|----------------|----|

| OP | d <sub>0</sub> | RA | RB  | d <sub>1</sub> | XO |

| OP | d <sub>0</sub> | RA | FRB | d <sub>1</sub> | XO |

| OP | RT             | RA | D   |                | XO |

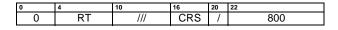

### 1.6.9 X6-Form

| 0  | 4  | 10 | 16 | 22   | 26 |

|----|----|----|----|------|----|

| OP | RT | RA | RB | CRT  | XO |

| OP | RT | RA | SH | CRT  | XO |

| OP | RT | RA | RB | / SH | XO |

## 1.6.10 D8-Form

| 0  | 4              | 7   | 10 | 16             | 24 |

|----|----------------|-----|----|----------------|----|

| OP | d <sub>1</sub> | SCL | RA | d <sub>0</sub> | XO |

| OP | d <sub>1</sub> | //  | RA | d <sub>0</sub> | XO |

## 1.6.11 I8-Form

| 0  | 4   | 8               | 16              | 24 |

|----|-----|-----------------|-----------------|----|

| OP | CRT | si <sub>1</sub> | si <sub>0</sub> | XO |

## 1.6.12 X8-Form

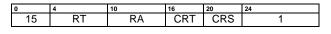

## 1.6.13 B10-Form

| 0  | 4    | 8  | 11   | 22 |

|----|------|----|------|----|

| OP | CRS  | BC | ADDR | XO |

| OP | ADDR |    |      | XO |

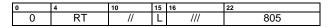

## 1.6.14 I10-Form

| 0  | 4  | 6               | 16              | 22 |

|----|----|-----------------|-----------------|----|

| OP | // | si <sub>1</sub> | si <sub>0</sub> | XO |

| 0  | 4   | 8               | 16              |

|----|-----|-----------------|-----------------|

| OP | CRT | si <sub>1</sub> | si <sub>0</sub> |

### 1.6.15 D10-Form

| 0  | 4              | 10 | 16             |   | 22 |

|----|----------------|----|----------------|---|----|

| OP | d <sub>1</sub> | RA | d <sub>0</sub> | / | XO |

## 1.6.16 X10-Form

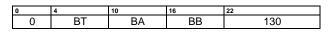

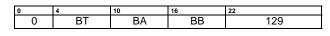

| 0  | 4 6 8               | 10 12 14            | 16 18 20         | 22 |

|----|---------------------|---------------------|------------------|----|

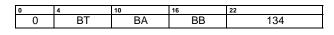

| OP | BT                  | BA                  | BB               | XO |

| OP | RT                  | RA                  | RB               | XO |

| OP | FRT                 | FRA                 | FRB              | XO |

| OP | CRT //              | FRA                 | FRB              | XO |

| OP | CRT / L             | RA                  | RB               | XO |

| OP | RT                  | RA                  | CRT //           | XO |

| OP | TO /                | RA                  | RB               | XO |

| OP | FRT                 | FRA                 | ///              | XO |

| OP | FRT                 | RA                  | ///              | XO |

| OP | RT                  | FRA                 | ///              | XO |

| OP | RT                  | RA                  | // XM            | XO |

| OP | RT                  | ///                 | FM               | ХО |

| OP | RT                  | RA                  | CRT XM           | XO |

| OP | RT                  | ///                 | // XM            | XO |

| OP | // spt <sub>1</sub> | RA                  | spt <sub>0</sub> | ХО |

| OP | RT                  | // sps <sub>1</sub> | sps <sub>0</sub> | ХО |

| OP | ///                 | ///                 |                  | XO |

| OP | CRT //              | RA                  | FM               | XO |

| OP | CRT //              | // BFI              | BFT //           | XO |

| OP | RT                  | ///                 | CRT //           | XO |

| OP | / FBT               | ///                 | CRT //           | XO |

| OP | RT                  | RA                  | ///              | XO |

| OP | TO /                | RA                  |                  | XO |

| OP | RT                  | ///                 | CRS //           | XO |

| OP | CRT //              | RA                  | ///              | XO |

| OP | CRT //              | ///                 | CRS //           | XO |

| OP | CRT //              | ///                 | CRI //           | ХО |

| OP | CRT //              | ///                 | BFS //           | XO |

| OP | RT                  | /// L               | ///              | ХО |

| OP | ///                 | /// L               | RB               | XO |

| OP | RT                  | ///                 | ///              | ХО |

| OP | ///                 | RA                  | ///              | XO |

|    | BRT //              | BRS //              | ///              | ХО |

| OP | CRT //              |                     | ///              | XO |

## **1.7 Instruction Fields**

#### ADDR(4:29 or 6:29)

Field used to specify the target address of a *Branch* instruction.

#### ADDR(4:21)

Field used to specify the block address of an *Instruction Cache* instruction.

#### ADDR(11:21)

Field used to specify the target address of a *Skip* instruction.

#### BA(10:15) and BB(16:21)

Field used to specify a bit in CR to be used as a source.

#### BC(8:10)

Field used to specify the condition tested in a *Skip* instruction.

#### BFI(12:15)

Field used to specify a 4-bit constant in a *Move to FPSCR* instruction.

#### BFS(16:18) and BFT(16,18)

Fields used to specify, respectively, a source and destination field in FPSCR.

#### BRS(10:11)

Field used to specify a branch register to be used as the source of an operation.

#### BRT(4:5)

Field used to specify a branch register to be used as the target of an operation.

#### BS(24:26)

Field used to specify an 8-bit (byte) portion of a register to be used as the target of byte immediate operations.

#### BT(4:9)

Field used to specify a bit in CR to be used as the target of the result of an instruction.

#### CB(22:27)

Field used to specify a bit in CR to be used as a source in the *Select* instructions.

#### CRI(16:19)

Field used to specify a 4-bit constant in a *Move to CR* instruction.

#### CRS(4:7, 16:19 or 20:23)

Field used to specify a field in CR used as a source operand.

#### CRT(4:7, 16:19, or 22:25)

Field used to specify a field in CR used as a target.

#### D(16:20||4:9, 16:23||4:6, 4:9||22:26 or 16:26)

Immediate field specifying an 11-bit unsigned integer which is used as the displacement for *storage access* instructions.

#### DL(16:26||10:15)

Immediate field specifying an 17-bit unsigned integer which is used as the displacement for *Load Table of Contents* instructions.

#### FBT(5:9)

Field used to specify a bit in FPSCR to be used as the target of the result of an instruction.

#### FM(16:21)

Field mask used to specify fields of FPSCR.

#### FRA(10:15), FRB(16:21) and FRC(22:27)

Fields used to specify a FPR as a source of an operation.

#### FRT(4:9)

Field used to specify a FPR as a target of an operation.

#### IA(10:15) and IB(16:21)

6-bit signed immediate value used in the *Select* instructions.

#### L(9 or 15)

Field used to specify whether certain instructions use 64-bit or 32-bit numbers, and to specify whether certain instructions use the most- or least-significant 32bits of a register.

#### MB(22:26, or 22:27)

Field used to specify the first 1-bit of a 64-bit mask.

#### ME(27:31, 27:30||16, or 22:27)

Field used to specify the last 1-bit of a 64-bit mask.

#### OP(0:3)

Primary opcode field

#### RA(10:15) and RB(16:21)

Fields used to specify a GPR as a source of an operation.

#### RT(4:9)

Field used to specify a GPR as a target of an operation.

#### SBI(16:23)

Immediate field used to specify an 8-bit signed integer.

#### SCL(7:9)

Field used to specify the level of storage for *Touch* instructions.

#### SF(27)

Single-bit field used to specify a speculative *Load* operation.

#### SH(16:21, 17:21, or 23:25)

Field used to specify a shift amount.

## SI(16:31, 16:30||8, 16:23||8:15, or 16:21||6:15)

Immediate field used to specify a 16-bit signed integer.

#### SPS(16:21||12:15)

Field used to specify a Special Purpose Register as a source of an operation.

#### SPT(16:21||6:9)

Field used to specify a Special Purpose Register as a target of an operation.

#### TO(4:8)

Field used to specify conditions on which to trap.

#### UBI(16:23)

Immediate field used to specify an 8-bit unsigned integer.

#### UI(16:31 or 16:30||8)

Immediate field used to specify a 16-bit unsigned integer.

XO(22:31, 24:31, 26:31, 27:31, 28:31, 30:31 or 31) Extended opcode field.

#### XM(20:21)

Field mask used to specify fields of XSR.

## **1.8 Classes of Instructions**

Any primitive instruction falls into exactly one of the following three classes:

- Defined

- Reserved

- Illegal

The class is determined by examining the opcode and the extended opcode, if any. If the opcode, or combination of opcode and extended opcode, is not that of a defined instruction nor of a reserved instruction, the instruction is illegal.

Some instructions are defined only for 64-bit implementations and a few are defined only for 32-bit implementations (see Section 1.8.2, "Illegal Instruction Class," on page 17). With the exception of these, a given instruction is in the same class for all implementations of the ForestaPC Architecture. In future versions of this architecture, instructions that are now illegal may become defined (by being added to the architecture) or reserved. Similarly, instructions that are now reserved may become defined.

## **1.8.1 Defined Instruction Class**

This class of instructions contains all the instructions defined in the ForestaPC User Instruction Set Architecture, ForestaPC Virtual Environment Architecture, and ForestaPC Operating Environment Architecture.

Defined instructions are guaranteed to be supported in all implementations, except as stated in the instruction descriptions. (The exceptions are instructions that are supported only in 64-bit implementations or only in 32-bit implementations.)

A defined instruction can have invalid forms, as described in Section 1.9, "Invalid Instruction Forms," on page 17.

## **1.8.2 Illegal Instruction Class**

For 64-bit implementations, this class includes all instructions that are defined only for 32-bit implementations. For 32-bit implementations, it includes all instructions that are defined only for 64-bit implementations.

Excluding instructions that are defined for one type of implementation but not the other, illegal instructions are available for future extensions of the ForestaPC architecture; that is, some future version of the ForestaPC architec-

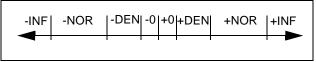

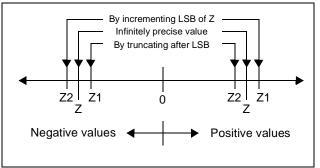

ture may define any of these instructions to perform new functions.