# **IBM Research Report**

# VESA Digital Packet Video Link (DPVL) Standard and Its Applications

# K. R. Schleupen, S. E. Millman

IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598

**T. Matsui** EIZO NANAO Corporation Matto, Ishikawa Japan

## **R. Feuerstein, P. Borberg** IBM Germany (IGS) Wuerzburg, Germany

Research Division Almaden - Austin - Beijing - Haifa - India - T. J. Watson - Tokyo - Zurich

LIMITED DISTRIBUTION NOTICE: This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. Ithas been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distributionoutside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g. payment of royalties). Copies may be requested from IBM T. J. Watson Research Center, P. O. Box 218, Yorktown Heights, NY 10598 USA (email: reports@us.ibm.com). Some reports are available on the internet at <a href="http://domino.watson.ibm.com/library/CyberDig.nsf/home">http://domino.watson.ibm.com/library/CyberDig.nsf/home</a>

### 10.1: VESA Digital Packet Video Link (DPVL) Standard and its Applications

K.R. Schleupen and S.E. Millman

IBM TJ Watson Research Center, Yorktown Heights, NY, USA e-mail: kais@us.ibm.com,

millman@us.ibm.com,

T. Matsui

EIZO NANAO Corp., Matto, Ishikawa, Japan e-mail: takashi\_matsui@attglobal.net

R. Feuerstein and P. Borberg

IBM Germany (IGS), Wuerzburg, Germany e-mail: Rainer.Feuerstein@de.ibm.com, borberg@de.ibm.com

#### Abstract

DPVL is a high-level video stream protocol which uses bandwidth more efficiently and therefore reduces system power consumption. The standard defines video-packet structures, a capability management scheme, and a monitor-control scheme. Recent applications for using DPVL include driving multiple LCD monitors from a single thin client.

#### 1. Introduction

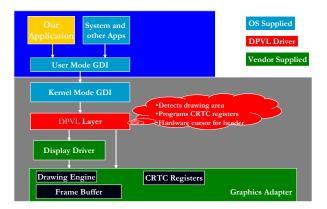

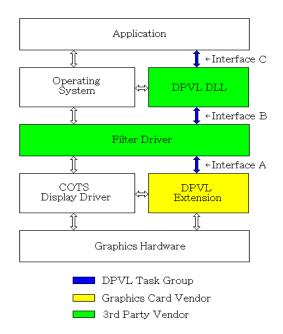

The work in the area of the Digital Packet Video Link (DPVL) technology started in 1998 when the first digital interfaces to display modules gained ground. In 1999, a DPVL working group composed of Japanese panel vendors Hitachi, IBM, Sharp and Toshiba was established. At the time the proposal was built specific hardware and assumed ASICs for both ends the graphics card side and the monitor side. However next generation graphics adapters came out at such a quick pace driven by the gaming business that it became obvious that the approach of having specific DPVL hardware on the host side would not deliver a sound business case. As a result, the DPVL working group in Japan was disolved in May 2001 and at the same time a new VESA DPVL Special Interest Group (SIG) was established driven by IBM Research. The proposal from IBM Research suggested leaving the graphics adapter physically unchanged and essentially be able to use existing graphic adapters on the market. Graphics Adapters (GA) are on a less than 6 month product cycle whereas monitors have a much longer lifetime until they will get replaced. To get around the issue of building specific graphics adapter hardware, IBM Research developed a DPVL hook driver for an off-theshelf GA which was placed between the display driver and the kernel mode GDI which is shown in Figure 1.

In April 2002, the VESA DPVL committee started its standardization work based on the above hardware assumptions. The standardization work was completed in April 2004 when DPVL Version 1 became a VESA standard [1]. Originally DPVL was developed to address the issue of driving high resolution monitors when multi-link DVI graphics adapters were not available. It was

demonstrated in 2001 [5] that a cheap off-the-shelf graphics adapter with 64MByte of memory and with a single DVI output can drive a DPVL prototype with 9.2Mpixel comfortably. However, it turned out that other market opportunities, such as driving multiple monitors from a single workstation might represent a much more attractive target. This paper focuses specifically on features of DPVL enabling multiple monitors and why certain industry sectors are very interested in applying DPVL from a form factor point of view.

Figure 1: DPVL Prototype Software Architecture

The DPVL protocol assumes that a DPVL compliant monitor will have a frame buffer to store the entire image displayed on the individual screen, so that the screen image integrity can be maintained by locally refreshing the display module though only the changed portions of parts of the whole desktop image are sent from the host.

#### 2. Multi-Monitor Support in DPVL

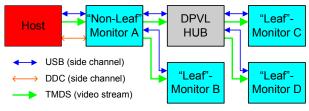

The VESA DPVL 1.0 standard [1] describes in detail all features in respect to multi-monitor support. In this section we focus on the most relevant ones necessary in support features. Figure 2 shows how a typical multi-monitor configuration in DPVL is defined. We distinguish between "Leaf" monitors and "Non-Leaf" monitors. A

"Non-Leaf"-Monitor should have one or more DVI outputs to be able to forward the video stream from the upstream node to the down stream nodes. The upstream node is either a host (PC, Thin Client, etc) or a hub or another "Non-Leaf" monitor. The host broadcasts the same video stream to all monitors.

DPVL Hub = DVI video repeater and USB hub

Figure 2: Multi-Monitor Configuration in DPVL

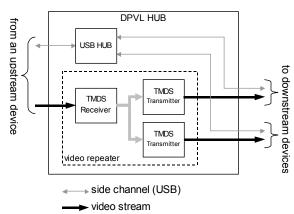

The DPVL protocol uses USB (Universal Serial Bus) for monitor capability management and for monitor control in multi-monitor configuration because DDC on DVI is only defined as a point-to-point interface, not a bus. The DDC channel is only available between the host system and the primary "Non-Leaf" monitor or hub. If it is a hub then the DDC channel will be routed through the hub to the primary output channel. That way in all cases at least one monitor is actively connected to the host system and can even show raster scan images (non-DVPL mode) if the host system should be in BIOS mode (during booting) or getting a blue screen (after OS crashed). The primary monitor is detected by comparing the EDIDs from the DDC channel with those received by the USB channel. Figure 3 shows an example of a DPVL hub which includes one TMDS receiver and two or more TMDS transmitters. The hub incorporates also a USB hub with an equal number of USB channels to downstream devices. Caution is necessary not to daisy-chain too many hubs or "Non-Leaf" nodes due to DVI jitter requirements.

Figure 3: Example of a DPVL HUB

Connection management is done via USB. If the absence of the DDC +5V is detected by each monitor, it informs the host of the disconnection as "Device disconnected" via the appropriate USB channel.

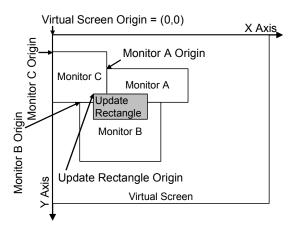

In multi-monitor configurations, the host manages a single large virtual screen, as shown in Figure 4. Each monitor is mapped to a part of the virtual screen. The host assigns the monitor origin to each monitor by using USB. Each monitor origin is set relative to the virtual screen origin, which is always (0,0). The origin of each video packet is also relative to the virtual screen origin. Each monitor examines the video stream and displays the video image that corresponds to the partial screen assigned to it.

Figure 4: Virtual Screen for Multi-Monitor Configurations in DPVL

In the example shown in Figure 4, monitors A, B and C receive the same video packet. Each monitor analyzes the packet header and captures only the part of the video packet that overlaps with its assigned region, while ignoring the rest. The host chooses a common transmission timing that all cascaded monitors support by reading out the DPVL-EXT (DPVL-Extension) blocks in the EDID (Extended Display Identification Data) of the individual monitors. DPVL-EXT is a data structure which allows a DPVL-enabled monitor to inform the host about its capabilities and features which are not included in the 128-byte base EDID structure. The DPVL-EXT block is an E-EDID (Enhanced Extended Display Identification Data) Release A-compliant extension block and requires the use of an EDID 1.3 data structure (or newer) as defined in the VESA E-EDID standard [8]. The DPVL-EXT contains the conformance level information, the transmission timing information, the native timing information of the display module, the frame buffer capability information and the capability information related to Basic Packets and Extended Packets [2][3].

#### 3. Launching Path for DPVL

In May 2004 during SID in Seattle, three companies (EIZO NANAO, IBM and TechSource) demonstrated with their DPVL prototypes interoperability [2] according to the published standard [1]. Since then more technical refinement in the DPVL implementations was executed and the issue of the standardization of the software interface was addressed. The DPVL standard became available for download in June 2004 and it gives interested organizations the opportunity to build prototypes based on this final version.

#### **3.1** Target an Industry Sector for DPVL

It became clear that multi-monitor applications would be the first market to target for DPVL. One potential market we targeted is the market of financial traders which also offers attractive quantities. The use of thin clients on the trading floor is very attractive because of low power consumption, small space usage and low levels of noise because thin clients have no fans. Due to the form factor of thin clients only a limited number of multi-head graphics card without fans fit into it and usually the number of monitors connected cannot be greater than two per thin client. Power requirements have to be reviewed very carefully in order not to overload the thin client's internal power supply and not to exceed its thermal requirements. Using DPVL with an off-the-shelf PCI graphics adapter in a thin client offers not only the lowest option for power consumption but it can also be easily extended by another monitor which is more difficult to do with multi-head graphic adapters.

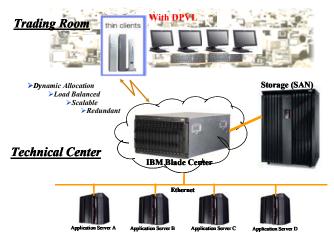

Figure 5 shows the use of DPVL in the Virtual Client Concept (VCC) for trading floors.

Figure 5: DPVL in the Virtual Client Concept (VCC)

#### **3.2 Define DPVL Software Interface**

While targeting specifically one single industry sector first with DPVL it was obvious that newly published DPVL standard alone defining its protocol would not solve the classic chicken and egg problem between monitor and graphic card manufacturers in support of availability of DPVL software drivers. Therefore, a DPVL-SI (Software Interface) task group was formed within VESA with the incentive to help proliferation of DPVL displays by allowing the majority of software to be developed in a device independent way. The mission of the task group is to define the software interfaces between DPVL handler and display driver (driver interface), as well as between the DPVL handler and applications (application interface). The proposed DPVL-SI standard is currently in committee review till November 8<sup>th</sup>, 2005.

Figure 6 shows the Display Driver interface in the MS Windows<sup>TM</sup> environment. Under MS Windows<sup>TM</sup> the DPVL Handler may be either a filter driver which resides in kernel mode on top of the display driver or a user mode DLL which resides in user mode and dispatches commands to the display driver. In addition, a combination of kernel mode filter driver and a DLL can also be envisioned.

Figure 6: Display Driver Interface with DPVL

The blue arrows in figure 6 indicate the standardization effort in the VESA DPVL Task Group, whereas the filter driver &DLL and the DPVL Extension are intended to be provided by 3<sup>rd</sup> party vendor and graphic card vendor, respectively.

#### 4. Conclusion

DPVL Version 1 became available as a downloadable VESA standard in June 2004. The VESA DPVL-SI (Software Interface) task group was formed in July 2004 and the proposed standard is currently in committee review. In addition a new Packetized Video task group was formed to create a standard which allows hosts to send display data over any high speed data channel which both the host and the display make available which also allows the remoting of I/O devices. One important future application are network-attached ultra-thin low-cost clients which eventually could be integrated into the monitor itself.

#### 5. Acknowledgements

We would like to thank the members of the VESA Display System committee (A. d'Hautecourt, D. Glen, J. Hosek, J. Irwin, Z. Lai, J. Lamm, S. McGowan, I. Miller, T. Miller, M. Ohara, L. Pierson, P. Robertson, D. Tran, J. Webb, G. Wiley, and E. Wogsberg) without whom this standard would not have been possible. Furthermore, we would like to thank the members of the VESA DPVL-SI task group committee (M. Anderson, M. Andrews, R. Baratto, A. Chitre, A. d'Hautecourt, S. Hussain, J. Lamm, S. McGowan, P. Merritt, I. Miller, J. Nieh, M. Stockfisch, J. Webb, E. Wogsberg, and W. Young) without whom the draft for the DPVL software interface proposed standard would not have been possible.

#### 6. References

- [1] "VESA Digital Packet Video Link (DPVL) Standard Version 1", http://www.vesa.org/summary/sumdpvl.mht.

- [2] Millman, S. et al, "Update to VESA Digital Packet Video Link (DPVL) proposed Standard", SID '04 Digest.

- [3] Lamm, J. "Invited Paper: Digital Packet Video Link A VESA Proposed Standard", SID' 03 Digest pp.1021-1023.

- [4] Ohara, M. et al, "Invited Paper: Recent Progress and Future Trend of Ultra-High-Resolution Large-Sized TFT-LCD Monitor Electronics", SID '02 Digest pp 168-171.

- [5] Ohara, M. et al. "Digital PV Link Light: A Simple Video Interface for High-Resolution Display", VESA Display Interfaces 2001.

- [6] Mamiya, J. et al. "Invited Paper: Digital PV Link for a Next-Generation Video Interface, and Its System Architecture", SID'00 Digest, pp. 38-41.

- [7] M. Ohara et al, "Digital Link: High Functional Digital Monitor Interface", SID'99 Digest.

- [8] "VESA E-EDID EEPROM Standard Version 1", http://www.vesa.org/summary/sumeedideeprom.mht