# **IBM Research Report**

# **Application Note: FPGA to IBM Power Processor Interface Setup**

# **Ibrahim Ouda**

IBM Systems &Technology Group 3605 Highway 52 N Rochester, MN 55901-1407

# Kai Schleupen

IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598

# Application Note FPGA to IBM Power Processor Interface Setup

#### Document Name: PowerXCell\_FlexIO\_GTP\_app\_note\_rel1.0 Date: June 27, 2008

#### Owner: Ibrahim Ouda Prepared by: Ibrahim Ouda and Kai Schleupen

#### IBM System&Technology Group and IBM Research

#### Sites: Rochester, MN and Yorktown Heights, NY USA

© Copyright International Business Machines Corporation 2008

© Copyright International Business Machines Corporation 2008.

All Rights Reserved. Printed in the United States of America in June 2008

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM Logo

All information contained in this document is subject to change without notice. The prototype described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

# **Table of Contents**

|   | Abstract                                                              |    |

|---|-----------------------------------------------------------------------|----|

| 2 | Introductions                                                         | 4  |

|   | 2.1 FlexIOTM - The Industry's Fastest Processor Bus Interface         | 4  |

|   | 2.2 Xilinx                                                            | 6  |

|   | 2.3 IBM Hardware used for bring-up of FlexIOTM to RocketIOTM GTP link | 8  |

| 3 | RocketIO GTP configuration.                                           | 10 |

|   | 3.1 RocketIO GTP Transceiver Wizard Screen Shots                      | 10 |

|   | 3.2 Manual Edit To Source File                                        | 22 |

|   | 3.3 Clocking                                                          | 23 |

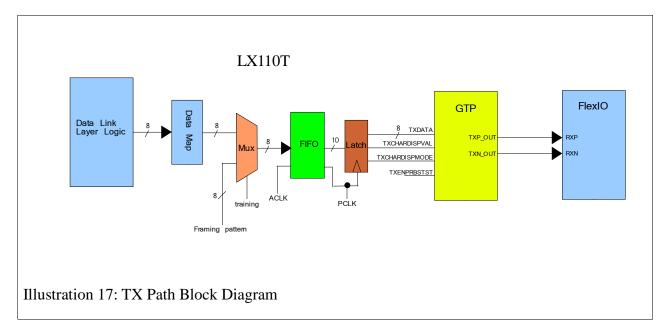

| 4 | TX Logic                                                              | 24 |

|   | 4.1 Data Link Layer Logic                                             | 24 |

|   | 4.2 Data Map                                                          | 24 |

|   | 4.3 Mux                                                               | 24 |

|   | 4.4 FIFO                                                              | 25 |

|   | 4.5 GTP                                                               | 25 |

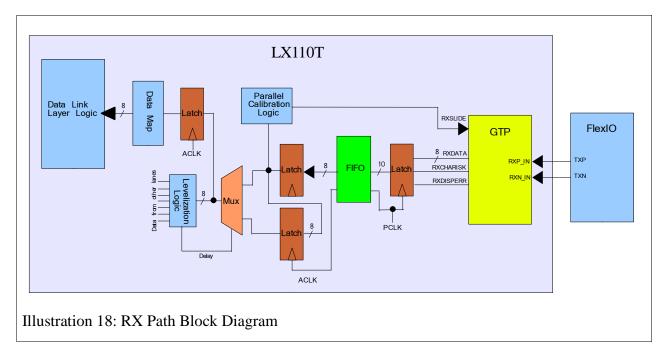

| 5 | RX Logic                                                              | 26 |

|   | 5.1 GTP                                                               |    |

|   | 5.2 FIFO                                                              | 26 |

|   | 5.3 Parallel Calibration                                              | 27 |

|   | 5.4 Levelization Logic                                                | 27 |

| 6 | Link Training                                                         |    |

|   | 6.1 Phase Calibration                                                 | 28 |

|   | 6.2 Parallel Calibration                                              | 29 |

|   | 6.3 Levelization Calibration                                          | 29 |

| 7 | GTP Electrical Characteristics Settings                               | 30 |

|   | Conclusion                                                            |    |

| 9 | Contact information for the application note                          | 31 |

# 1 Abstract

This application note describes the setup within the Xilinx FPGA tools to be able to establish a highbandwidth interface between an IBM Power Processor and the latest Xilinx FPGAs via an interface implementation from Rambus Inc. It has been currently successfully evaluated and tested on a system prototyping platform up to a data rate of 3Gbit/sec per lane and can be expanded to multiple bytes. It represents one of the fastest coherent/non-coherent processor to FPGA interfaces available in the industry.

# 2 Introductions

### 2.1 FlexIO<sup>™1</sup> - The Industry's Fastest Processor Bus Interface

The Rambus<sup>®</sup> FlexIO family of processor bus interfaces closes the critical I/O to logic speed performance gap and represents a significant breakthrough in parallel chip-to-chip interface technology. Now this technology is available on FPGAs. This application note describes how to configure Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 FPGA to interface to FlexIO.

FlexIO offers data rates of 400MHz to 8 GHz which is up to ten times faster than today's best-of-class processor busses, while reducing overall package, board, and system costs. Optimized for intra-board environments, it provides an ideal low-latency and low-power solution for high-volume, low-cost applications, including processor (e.g. Cell Broadband Engine<sup>TM 2</sup> and IBM's PowerXCell<sup>TM 3</sup> 8i Processor), chipset and network chip connections for a broad range of applications like High-Performance Computing. For ASIC implementations, the FlexIO processor bus is optionally backwards compatible to existing LVDS-based standards, including HyperTransport<sup>TM 4</sup>, SPI-4 and RapidIO<sup>TM 5</sup>, allowing easy integration into next generation products, while providing a path to higher levels of performance. The FPGA implementation of the FlexIO processor bus interface provides a complete physical layer solution for both standards based and proprietary applications. Rambus provides directly both the physical layer and logic layer IP for ASIC applications.

In addition to breakthrough bandwidth, FlexIO processor bus interfaces provide flexibility, simplicity and savings in system design through three innovative building blocks: FlexPhase<sup>™</sup> circuit technology is a major departure from traditional circuit technologies. It enables precise, per bit, on-chip alignment of data and clock, eliminating the need for PCB trace length matching and PCB timing constraints. This results in logic systems that are simpler, more compact, lower in cost, and capable of multi-GHz data rates. DRSL (Differential Rambus Signaling Levels) with LVDS (Low Voltage Differential Signaling) enables backward compatibility. DRSL is a differential signaling technology available in bi-directional and uni-directional versions that offers a high-performance, low power, costeffective solution for transmitting data on and off chip. DRSL uses a variable signal swing as low as 200mV, enabling low-power operation, reduced electromagnetic radiation (EMR) and scalability to lower process voltages in the future. Variable Date Rate (VDR) delivers data rates of 1-to-10 times the speed of the clock, supporting a wide range of system clocks and data rates ranging from 400 MHz - 8 GHz.

The FlexIO family of high performance processor bus interfaces extends the versatility of Rambus'

<sup>1</sup> FlexIO is a trademark of Rambus Inc.

<sup>2</sup> Cell Broadband Engine is a registered trademark of Sony Computer Entertainment, Inc

<sup>3</sup> PowerXCell is a registered trademark of IBM Corp

<sup>4</sup> Hypertransport is a registered trademark of the HyperTransport Technology Consortium

<sup>5</sup> RapidIO is a registered trademark of the RapidIO Trade Association

logic interface solutions and complements the Rambus(tm) high-performance serial link interface family. FlexIO interfaces are ideal for intra-board applications with shorter-distance (up to 15") and lower-distortion interconnects. In these applications, FlexIO processor busses provide lower power and lower latency than traditional serial link solutions

### 2.2 Xilinx

Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 multi-platform FPGAs offer built-in serial connectivity with two varieties of transceivers. RocketIO<sup>TM 6</sup> GTP transceivers found on Virtex-5 LXT and SXT FPGA platform devices support line rates up to 3.75Gpbs with the industry's lowest power consumption. These transceivers support a variety of standards, such as PCIe<sup>TM 7</sup>, RapidIO<sup>®8</sup>, Gigabit Ethernet, XAUI<sup>TM 9</sup>, InfiniBandt<sup>TM10</sup>, Fibre Channel<sup>TM 11</sup>, SATA, HD-SDI, SONET, Interlaken, and SFI-5.

For protocols requiring higher line rates, including future FlexIO interfaces, Virtex-5 FXT FPGA platform devices offer RocketIO GTX transceivers which deliver power-efficient connectivity up to 6.5Gbps. Cross platform pin compatibility eases design upgrades from GTP to GTX transceivers.

The RocketIO GTP transceiver is highly configurable and tightly integrated with the programmable logic resources of the FPGA. Key features include:

- Line rates from 100 Mb/s to 3.75 Gb/s

- Less than 100 mW typical power consumption at 3.2 Gbps

- Current Mode Logic (CML) serial drivers/buffers with configurable termination, voltage swing, and coupling

- Programmable TX pre-emphasis and RX equalization for optimized signal integrity

- Optional built-in PCS features, such as 8B/10B encoding, comma alignment, channel bonding, and clock correction

- CRC generation and checking

- User dynamic reconfiguration using secondary configuration bus

- Spread-spectrum clocking support

- Built-in PRBS Generators and Checkers

GTP transceivers are placed as dual transceiver GTP\_DUAL tiles in Virtex-5 LXT and SXT platform devices. This configuration allows two transceivers to share a single PLL with the TX and RX functions of both, reducing size and power consumption.

<sup>6</sup> RocketIO is a registered trademark of Xilinx, Inc.

<sup>7</sup> PCIe is a registered trademark of PCI-SIG Corp.

<sup>8</sup> RapidIO is a regsistered trademark of the RapidIO Trade Association

<sup>9</sup> XAUI is a trademark of the 10Gigabit Ethernet Alliance XAUI Interoperability Group

<sup>10</sup> Infiniband is a registered trademark of systemI/O Inc.

<sup>11</sup> Fibre Channel is trademark of the Fibre Channel Industry Association

#### Documentation available from Xilinx:

For more information on Virtex-5 FPGAs visit <u>www.xilinx.com/virtex5</u>. There you will find links to product overview videos, technical documentation, design tools. and more.

The first-time RocketIO transceiver user is recommended to read *High-Speed Serial I/O Made Simple*, which discusses high-speed serial transceiver technology and its applications. A free download is available at <u>http://www.xilinx.com/publications/books/serialio/serialio-book.pdf</u>

Virtex-5 family overview: <u>http://www.xilinx.com/support/documentation/data\_sheets/ds100.pdf</u> RocketIO GTP user guide: <u>http://www.xilinx.com/support/documentation/user\_guides/ug196.pdf</u> RocketIO GTX user guide: <u>http://www.xilinx.com/support/documentation/user\_guides/ug198.pdf</u>

### 2.3 IBM Hardware used for bring-up of FlexIO<sup>™</sup> to RocketIO<sup>™</sup> GTP link

IBM developed a special prototype blade, called Chameleon Cell Blade, as a test platform for exploratory research and development of direct high-speed processor interfaces, accelerators, architectural studies and testing processor cores in a real firmware/software environment.

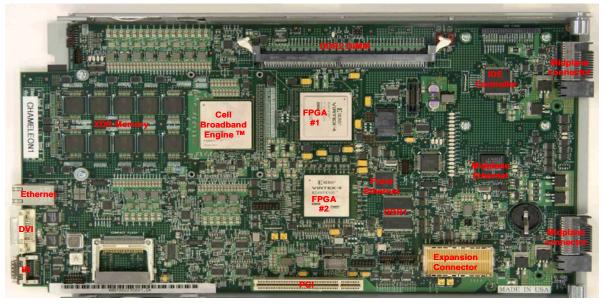

Illustration 1 shows a picture of the Chameleon Cell Blade prototype. Key components of the blade are the Cell Broadband Engine<sup>TM</sup>, XDR memory, DDR2 DIMM, and in this version two Xilinx Virtex-4<sup>TM</sup> FPGAs. The prototype is designed to fit a single-wide blade form factor. FPGA#1 interacts directly with the Cell Broadband Engine<sup>TM</sup> and is the main device for running exploratory logic. FPGA#2 establishes the system IO and therefore acts as a reconfigurable southbridge. This prototype blade uses a special high-speed expansion card connector to provide PCIe connectivity and routing one single byte of FlexIO<sup>TM</sup> from the Cell Broadband Engine<sup>TM</sup> to a high speed expansion card (HSEC) for experimental extensions. One of the extensions designed by IBM is a HSEC with a Xilinx FPGA. The same FlexIO<sup>TM</sup> to RocketIO<sup>TM</sup> GTP interface exists on IBM's PowerXCell<sup>TM</sup> 8i processor as well and was setup the same way.

Illustration 1: Photograph of the Chameleon Cell Blade V1.0

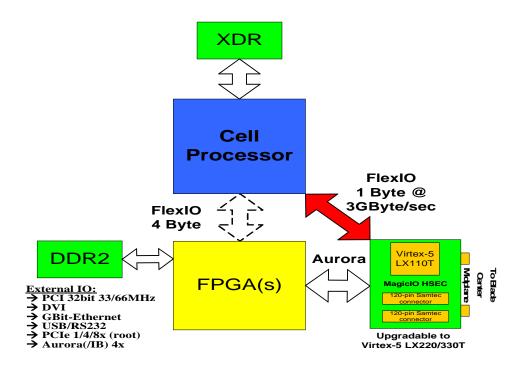

Illustration 2 shows a simplified block diagram of the bring-up platform for the setup, testing and evaluation of the FlexIO<sup>TM</sup> to FPGA GTP interface whose implementation is described the the following chapters.

Illustration 3 shows a photograph of this special HSEC, called MagicIO HSEC, which contains as a key component: a Virtex-5<sup>TM</sup> LX110T Xilinx FPGA. The FPGA provides versatility to the expansion card function. This HSEC was part of the setup establishing a high-speed interface between the Cell Broadband Engine<sup>TM</sup> and the FPGA's GTPs. The average trace length on the board (Chameleon and

HSEC combined) for this link is about 16" routed on a standard FR4 PCB.

Illustration 2: Simplified block diagram of Chameleon Cell Blade with MagicIO HSEC

Illustration 3: Photo of the MagicIO HSEC

# 3 RocketIO GTP configuration

#### 3.1 RocketIO GTP Transceiver Wizard Screen Shots

The following are the screen shots from the RocketIO GTP Transceiver Wizard for the setup used in the prototype hardware for the link. In the prototype implementation GTPs 4 - 7 are used. For board specific issue, the dedicated GTP clock pins were not used for this implementation. Using the GTP clock pins will improve the clocking structure and clock quality. The clocking implementation is described in a later section.

| ogiCQRE                   | RocketlO GTP Wizard                                                                                                                                                                     | v1.     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                           |                                                                                                                                                                                         | 1.1.2.6 |

| Component Name rocket     | o                                                                                                                                                                                       |         |

| -Select Tiles and Referen | ce Clocks                                                                                                                                                                               |         |

|                           | GTP_DUAL (Location) REFCLK source<br>(not applicable)                                                                                                                                   |         |

|                           | Transceivers selected (2 per GTP_DUAL):                                                                                                                                                 |         |

|                           | The individual transceivers in each GTP_DUAL tile will<br>receive the same settings. Use the pages that follow to<br>disable individual transceivers and to apply protocol<br>settings. |         |

|                           |                                                                                                                                                                                         |         |

Illustration 4: RocketIO GTP Wizard screen 1 of 12

#### GTP\_DUAL\_X0Y4, GTP\_DUAL\_X0Y5, GTP\_DUAL\_X0Y6 and GTP\_DUAL\_X0Y7 are selected.

Select the proper REFCLK source if using the GTP clock pins. In this implementation the default value is selected.

| ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ommended) 300.00 💌 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Use Dynamic Reconfiguration Port<br>Use REFCLKOUT Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Gbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>v</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Gbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| to a fill of the f |

| Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Illustration 5: RocketIO GTP Wizard screen 2 of 12

Using internal Data Width of 10 bits. Target line rate is set to 3.00 Gbps. Reference clock is set to 300 MHz. To be able to modify GTP internal settings through the GTP registers, select the option to "Use Dynamic Reconfiguration Port". Select the option to "Start from Scratch for the GTP Protocol Template. Set the TX Settings to use 3Gbps line rate, 8B/10B Encoding and 8 bits for the data path width. The FlexIO link does not use any encoding but the the 8B/10B selection is needed to get the proper internal data width. The internal 8B/10B circuit will be bypassed and not used. The RX settings

are the same as the TX settings. For GTP1 Protocol Template, select the option to use GTP0 settings since both GTPs are identical. The 8B/10B selection above along with the data path width of 8 bits for the TX and RX will enable the user to connect the 10 bits manually outside of the RocketIO GTP wrapper. This method was used originally due to a Wizard issue which caused bad bit connection inside the RocketIO GTP wrapper. An alternative way is to use no encoding and 10 bits for data path width and the Wizard will make the proper connection internally.

| gi <mark>C</mark> QRE                                                                          | RocketIO GTP Wizard                           | v1            |

|------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|

|                                                                                                | 8b/10b O                                      | ptional Ports |

| GTPO                                                                                           |                                               |               |

| TX<br>TXBYPASS8B10B<br>TXCHARDISPMODE<br>TXCHARDISPVAL<br>TXCHARDISPVAL<br>TXKERR<br>TXRUNDISP | RX<br>RXCHARISCOMMA<br>RXCHARISK<br>RXRUNDISP |               |

| GTP1                                                                                           | 24                                            |               |

| TX<br>TXBYPASS8B10B<br>TXCHARDISPMODE<br>TXCHARDISPVAL<br>TXKERR<br>TXRUNDISP                  | RX<br>RXCHARISCOMMA<br>RXCHARISK<br>RXRUNDISP |               |

| <u>.</u>                                                                                       |                                               |               |

|                                                                                                |                                               |               |

|                                                                                                |                                               |               |

|                                                                                                |                                               |               |

|                                                                                                |                                               |               |

|                                                                                                |                                               |               |

|                                                                                                |                                               |               |

Illustration 6: RocketIO GTP Wizard screen 3 of 12

For GTP TX settings, select the following ports:

- TXBYPASS8B10B. This is used to bypass the internal 8B/10B circuit.

- TXCHARDISPMODE. This will be used for bit 9 of TX link 10 bit data.

- TXCHARDISPVAL. This will be used for bit 8 of TX link 10 bit data.

For GTP RX settings, select RXCHARISK port which will be used for bit 8 of RX link data. Bit 9 of the TX link data will use RXDISPERR port which is available but not selectable from the RocketIO GTP Wizard.

| iC      | RE                                  | RocketlO                              | GTP Wizard                               | đ       |

|---------|-------------------------------------|---------------------------------------|------------------------------------------|---------|

|         |                                     |                                       | Latency, Buffering, and (                | Clockin |

| TX PCS  | S/PMA Phase Alignment -             |                                       |                                          |         |

| Use T   | X Phase Alignment circuit           | to minimize lane skew and/or reduce   | TX latency                               |         |

| O Us    | se TX Buffer (default)              | ۲                                     | ) Use TX Phase Alignment circuit         |         |

| GTP0-   |                                     |                                       |                                          |         |

| RX F    | TXUSRCLK Source<br>CS/PMA Alignment | REFCLKOUT                             | RXUSRCLK Source TXOUTCLK                 | ~       |

| $\odot$ | Use RX Buffer (default, er          | ables clock correction and channel l  | bonding)                                 |         |

| 0       | Use RX Phase Alignment              | (low latency, receive clock frequency | y must match its transmitter's clock)    |         |

| Optic   | onal Ports                          |                                       |                                          |         |

|         | RXRESET                             | TXOUTCLK                              | TXBUFSTATUS                              |         |

|         | RXRECCLK                            | TXRESET                               | TXINHIBIT                                |         |

|         | RXBUFSTATUS                         | TXPOLARITY                            |                                          |         |

|         | RXBUFRESET                          | TXENPRBSTST (PRBS                     | transmission control)                    |         |

|         |                                     |                                       |                                          |         |

| GTP1-   | TXUSRCLK Source                     | DEFCUROUT                             | RXUSRCLK Source TXOUTCLK                 |         |

| RX P    | CS/PMA Alignment                    | REFCLKOUT                             | RAUSHELK Source TAUDICLK                 |         |

|         |                                     | ables clock correction and channel t  | pondina)                                 |         |

|         |                                     | (low latency, receive clock frequency | 5                                        |         |

| Ontio   | onal Ports                          |                                       |                                          |         |

|         | RXRESET                             | TXOUTCLK                              | TXBUFSTATUS                              |         |

|         | RXRECCLK                            | TXRESET                               | TXINHIBIT                                |         |

|         | RXBUFSTATUS                         | TXPOLARITY                            | 12500.000                                |         |

|         | RXBUFRESET                          | TXENPRBSTST (PRBS                     | transmission control)                    |         |

|         |                                     | · · · · · · · · · · · · · · · · · · · | en e |         |

Illustration 7: RocketIO GTP Wizard screen 4 of 12

The above selections are needed if the 8B/10B selection is made in the previous page. If no encoding is selected and 10 bit data path width, this page is not applicable.

For TX PCS/PMA Phase Alignment, select the option to use TX phase alignment circuit. For the RX PCS/PMA Alignment, select the option to use RX buffer. Select the following optional ports:

- RXRESET. Can be used to reset the RX block.

- RXBUFSTATUS. Used for debug in the initial implementation.

- RXBUFRESET. Used to reset the RX buffer. This is optional but recommended.

- TXRESET. Can be used to reset the TX block.

- TXENPRBSTST. Needed to enable PRBS pattern to be sent to the FlexIO during link phase calibration.

| Rock                                                                                                                                                                   | tetIO GTP Wizard                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| iTP0                                                                                                                                                                   | Preemphasis, Termination, and Equalization         |

| Preemphasis and Differential Swing                                                                                                                                     |                                                    |

| Transmitter swing turbo mode (increase swing by 10)                                                                                                                    | 2)                                                 |

| Preemphasis level Use TXPREEMPHASIS Port                                                                                                                               | Main driver differential swing Use TXDIFFCTRL Port |

| RX Equalization                                                                                                                                                        | RX Termination                                     |

| Use RX Equalization                                                                                                                                                    | Disable internal AC coupling                       |

| High-pass Filter Pole Location                                                                                                                                         | Termination Voltage                                |

| External resistor sets location     Use RXEQPOLE                                                                                                                       |                                                    |

| <ul> <li>Specify individual location</li> </ul>                                                                                                                        | * recommended value                                |

| Wideband/Highpass Ratio Use RXEQMIX Port                                                                                                                               |                                                    |

| Optional Ports                                                                                                                                                         |                                                    |

| RXCDRRESET                                                                                                                                                             | RXPOLARITY                                         |

| Preemphasis and Differential Swing                                                                                                                                     | ····                                               |

| Preemphasis level Use TXPREEMPHASIS Port 🔛                                                                                                                             | Main driver differential swing Use TXDIFFCTRL Port |

|                                                                                                                                                                        | RX Termination                                     |

| RX Equalization                                                                                                                                                        | Disable internal AC coupling                       |

| Use RX Equalization                                                                                                                                                    |                                                    |

| Use RX Equalization<br>High-pass Filter Pole Location                                                                                                                  |                                                    |

| Use RX Equalization                                                                                                                                                    | GND 2/3 VTTRX* • VTTRX                             |

| Use RX Equalization<br>High-pass Filter Pole Location<br>External resistor sets location<br>Use RXEQPOLE                                                               | GND 2/3 VTTRX* VTTRX                               |

| Use RX Equalization High-pass Filter Pole Location External resistor sets location Specify individual location Use RXEQPOLE                                            | GND 2/3 VTTRX VTTRX     recommended value          |

| Use RX Equalization<br>High-pass Filter Pole Location<br>External resistor sets location<br>Specify individual location<br>Wideband/Highpass Ratio Use RXEQMIX Port    | GND 2/3 VTTRX VTTRX     recommended value          |

| Use RX Equalization High-pass Filter Pole Location External resistor sets location Specify individual location Wideband/Highpass Ratio Use RXEQMIX Port Optional Ports | COND C/3 VTTRX VTTRX  recommended value            |

Illustration 8: RocketIO GTP Wizard screen 5 of 12

Select "Transmitter swing turbo" mode. To be able to easily modify the pre-emphasis level, select the option to "use TXPREEMPHASIS port". Select to use the TXDIFFCTRL port for the main driver differential swing.

Select RX Equalization options as shown and select the option to disable the internal AC coupling under "RX Termination".

| ose Sync 128 | utter                                                   |  |  |  |

|--------------|---------------------------------------------------------|--|--|--|

|              | Use PRBS Detector<br>PRBS Error Threshold 1             |  |  |  |

|              | PRBS Error Threshold 1 Errors Required to Lose Sync 128 |  |  |  |

|              | uffer Errors Required to Lose Sync 128                  |  |  |  |

|              | unter                                                   |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

|              |                                                         |  |  |  |

|              |                                                         |  |  |  |

|              | OOB Signal Detection PRBS                               |  |  |  |

|              | Use PRBS Detector                                       |  |  |  |

|              | PRBS Error Threshold 1                                  |  |  |  |

|              |                                                         |  |  |  |

|              |                                                         |  |  |  |

|              |                                                         |  |  |  |

|              |                                                         |  |  |  |

|              | uffer                                                   |  |  |  |

|              |                                                         |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

| ount by 1 8  | Good bytes to reduce Error Count by 1 8                 |  |  |  |

|              | unter                                                   |  |  |  |

Illustration 9: RocketIO GTP Wizard screen 6 of 12

The only modification to this screen is to select the option to use PRBS detector with PRBS error threshold of 1. This will be used during the GTP receive side phase calibration step.

|                                                     |            | RX Comma Alignme                                                                                                                                                                                                   |