# **IBM Research Report**

# **QPX Architecture:** Quad Processing eXtension to the Power ISA $^{TM}$

### Thomas Fox, Michael Gschwind, Jaime Moreno

(foxy, mkg, jhmoreno@us.ibm.com)

IBM Research Division

Thomas J. Watson Research Center

P.O. Box 218

Yorktown Heights, NY 10598

### **Contributors**

The following individuals contributed to an extensive degree to this architectural specification:

John Gunnels

Alexandre Eichenberger

**Daniel Prener**

Bruce Fleischer

### **Acknowledgements**

The following individuals played a significant role in the design of the Quad floating-point Processing Unit of the BQC compute chip in Blue Gene/Q:

Charles Wait

Thomas Roewer

Bernard Brezzo

### Chapter 1. Quad-Vector Floating-Point Facility Overview

This document defines the Blue Gene/Q Quad-Processing eXtension (QPX) to IBM's Power Instruction Set Architecture. Refer to IBM's Power ISA<sup>TM</sup> AS architecture document for descriptions of the base Power instruction set, the storage model, and related facilities available to the application programmer.

The computational model of the QPX architecture is a vector Single Instruction Multiple Data (SIMD) model with four execution slots and a register file containing 32 registers of 256 bits. Each of the 32 registers can be envisioned as containing four elements of 64 bits, whereby each of the execution slots operates on one vector element.

### 1.1 Notation

The following notation is specific to and used throughout the QPX Architecture document.

QRT, QRA, QRB, and QRC refer to Quad Floating-Point Registers, which are 256-bit vector registers containing four elements with 64 bits per element. The vector elements are numbered 0,1,2,3, with element 0 comprising bits 0:63, element 1 comprising bits 64:127, element 2 comprising bits 128:191, and element 3 comprising bits 192:255.

QRT<sup>x</sup> refers to element x of vector register QRT.

### Chapter 2. Quad-Vector Floating-Point Facility Registers

# 2.1 Quad-Vector Floating-Point Registers

Implementations of this architecture provide 32 Quad-vector floating-Point Registers (QPRs), named QPR0 through QPR31. The QPX instruction formats provide 5-bit fields for specifying the QPRs to be used in the execution of the instruction.

Scalar floating-point computational instructions, defined in the Power ISA, operate on element 0 QPRs, which serve as both the scalar FPRs for scalar instructions and the element 0 QPRs for vector instructions.

The figure below shows the Quad floating-point registers.

| OPR01              | OPR0 <sup>2</sup>  | QPR0 <sup>3</sup>                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------|

|                    | _                  | QPR1 <sup>3</sup>                                                         |

| QPRT               | QPR1-              | QPRT                                                                      |

|                    |                    |                                                                           |

|                    |                    |                                                                           |

| QPR30 <sup>1</sup> | QPR30 <sup>2</sup> | QPR30 <sup>3</sup>                                                        |

| QPR31 <sup>1</sup> | QPR31 <sup>2</sup> | QPR31 <sup>3</sup>                                                        |

|                    |                    | QPR1 <sup>1</sup> QPR1 <sup>2</sup> QPR30 <sup>1</sup> QPR30 <sup>2</sup> |

127 128

191 192

255

Figure 1. Quad Floating-Point Registers

# 2.2 Floating-Point Status and Control Register

The Floating-Point Exception Summary bits (32:34) and the Floating-Point Exception bits (35:44 and 53:55) of the FPSCR are never updated by QPX instructions, neither implicitly nor explicitly. The remaining status bits (45:51) are never updated by QPX instructions.

The Floating-Point Exception Enable bits (56:60) are ignored by all QPX instructions, which execute as if these bits were disabled. The Floating-Point Non-IEEE Mode (NI) bit (61) and the Floating-Point Rounding Control (RN) bits (62:63) of the FPSCR affect the operations on all four vector elements for QPX instructions.

### 2.3 Store Exception Enable Registers

Certain QPX store instructions provide a novel mechanism for the detection and indication of numerically exceptional conditions at the store interface.

A Store Indicate NaN Exception occurs when the source operand of a Store with Indicate instruction contains a NaN value. The Store Nan Exception Enable (SNEE) register enables the indication of such an exception. If an enabled Store Indicate NaN Exception occurs, the Auxiliary Processor bit of the Exception Syndrome Register is set (ESR[AP] = '1').

A Store Indicate Infinity Exception occurs when the source operand contains an Infinity value during a Store with Indicate instruction. The Store Infinity Exception Enable (SIEE) register enables the indication of such an exception. If an enabled Store Indicate Infinity Exception occurs, the Auxiliary Processor bit of the Exception Syndrome Register is set (ESR[AP] = '1').

The precedence of simultaneously occurring indication exceptions and memory fault exceptions is implementation defined.

### **Implementation Note**

In the QPU for BGQ, the following bits in the AXUCR0 Special Purpose Register contain the SNEE and SIEE state on a per thread basis:

```

axucr0(20) : Thread 0 SNEE

axucr0(21) : Thread 0 SIEE

axucr0(22) : Thread 1 SNEE

axucr0(23) : Thread 1 SIEE

axucr0(24) : Thread 2 SNEE

axucr0(25) : Thread 2 SIEE

axucr0(26) : Thread 3 SNEE

axucr0(27) : Thread 3 SIEE

```

## **Chapter 3. Scalar Instructions**

Scalar floating-point load instructions, defined in the Power ISA, cause a replication of the source data across all elements of the target register.

Scalar floating-point move, arithmetic, rounding and conversion, compare, and select instructions, defined in the Power ISA, are executed in execution slot 0. Source operands for these instructions are read from element 0 QPRs, while target results are written to element 0 QPRs. Target elements 1, 2, and 3 are left in an undefined state.

### Chapter 4. Quad-Vector Floating-Point Facility Instructions

### 4.1 Quad-Vector Floating-Point Load Instructions

# Quad-Vector Load Floating-point Single indeXed X-form

| qvlfsx  | QRT,RA,RB | (X=0) |

|---------|-----------|-------|

| qvlfsxa | QRT,RA,RB | (X=1) |

| 31 | QRT | RA | RB | 519 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{array}{lll} \text{if RA = 0 then } b \leftarrow 0 \\ \text{else} & b \leftarrow (\text{RA}) \\ \text{EA} \leftarrow (b + (\text{RB})) \& 0 \text{xFFFFFFFFFFFFF} \\ \text{MVAL} \leftarrow \text{MEM(EA, 16)} \\ \text{QRT}^0 \leftarrow \text{DOUBLE}(\text{MVAL}_{0:31}) \\ \text{QRT}^1 \leftarrow \text{DOUBLE}(\text{MVAL}_{32:63}) \\ \text{QRT}^2 \leftarrow \text{DOUBLE}(\text{MVAL}_{64:95}) \\ \text{QRT}^3 \leftarrow \text{DOUBLE}(\text{MVAL}_{96:127}) \\ \end{array}

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as four single-precision vector elements, converted to double-precision format, and placed into register QRT.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

# Quad-Vector Load Floating-point Single with Update indeXed X-form

| qvlfsux  | QRT,RA,RB | (X=0) |

|----------|-----------|-------|

| qvlfsuxa | QRT,RA,RB | (X=1) |

|   | 31 | QRT | RA | RB | 551 | Χ  |

|---|----|-----|----|----|-----|----|

| 0 |    | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as four single-precision vector elements, converted to double-precision format, and placed into register QRT.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

# Quad-Vector Load Floating-point Double indeXed X-form

| qvlfdx  | QRT,RA,RB | (X=0) |

|---------|-----------|-------|

| qvlfdxa | QRT,RA,RB | (X=1) |

|         |           |       |

| 31 | QRT | RA | RB | 583 | X  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

if RA = 0 then b \leftarrow 0 else b \leftarrow (RA) EA \leftarrow (b + (RB)) & 0xfffffffffffffff0QRT \leftarrow MEM(EA, 32)

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The 32 bytes in storage addressed by the 32-byte-aligned EA are interpreted as four double-precision vector elements, and placed into register QRT.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

#### **Special Registers Altered:**

None

# Quad-Vector Load Floating-point Double with Update indeXed X-form

| qvlfdux  | QRT,RA,RB | (X=0) |

|----------|-----------|-------|

| qvlfduxa | QRT,RA,RB | (X=1) |

|          |           |       |

| 31 | QRT | RA | RB | 615 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{split} \text{EA} &\leftarrow \text{((RA) + (RB))} \& \text{0xffffffffffe0} \\ \text{QRT} &\leftarrow \text{MEM(EA, 32)} \\ \text{RA} &\leftarrow \text{EA} \end{split}

```

Let the effective address (EA) be the sum (RA)+(RB).

The 32 bytes in storage addressed by the 32-byte-aligned EA are interpreted as four double-precision vector elements, and placed into register QRT.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

### **Special Registers Altered:**

# Quad-Vector Load Floating-point Complex Single indeXed

### X-form

### Quad-Vector Load Floating-point Complex Double indeXed X-form

| qvlfcsx  | QRT,RA,RB | (X=0) |

|----------|-----------|-------|

| qvlfcsxa | QRT,RA,RB | (X=1) |

| 31 | QRT | RA | RB | 7  | Х  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

The 8 bytes in storage addressed by the 8-byte-aligned EA are interpreted as two single-precision vector elements, converted to double-precision format, and replicated into register QRT.

If the X bit is set, and the address is not aligned on an 8-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

| qvlfcdx  | QRT,RA,RB | (X=0) |

|----------|-----------|-------|

| qvlfcdxa | QRT,RA,RB | (X=1) |

| 31 | QRT | RA | RB | 71 | Χ  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as two double-precision vector elements, and replicated into register ORT.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

### Quad-Vector Load Floating-point Complex Single with Update indeXed X-form

### qvlfcsux QRT,RA,RB (X=0) qvlfcsuxa QRT,RA,RB (X=1)

| 31 | QRT | RA | RB | 39 | Χ  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the sum (RA)+(RB).

The 8 bytes in storage addressed by the 8-byte-aligned EA are interpreted as two single-precision vector elements, converted to double-precision format, and replicated into register QRT.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 8-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

### Quad-Vector Load Floating-point Complex Double with Update indeXed X-form

$\begin{array}{lll} \text{qvlfcdux} & \text{QRT,RA,RB} & \text{(X=0)} \\ \text{qvlfcduxa} & \text{QRT,RA,RB} & \text{(X=1)} \\ \end{array}$

| 31 | QRT | RA | RB | 103 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as two double-precision vector elements, and replicated into register QRT.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

### Quad-Vector Load Floating-point as Integer Word Algebraic indeXed X-form

####

| 31 | QRT | RA | RB | 871 | X  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{array}{lll} \text{if RA = 0 then } b \leftarrow 0 \\ \text{else} & b \leftarrow (\text{RA}) \\ \text{EA} \leftarrow (b + (\text{RB})) \& 0 \text{xfffffffffffff} \\ \text{M} \leftarrow \text{MEM(EA, 16)} \\ \text{QRT}^0 \leftarrow {}^{32}(\text{M}_0) & \parallel \text{M}_{0:31} \\ \text{QRT}^1 \leftarrow {}^{32}(\text{M}_{32}) & \parallel \text{M}_{32:63} \\ \text{QRT}^2 \leftarrow {}^{32}(\text{M}_{64}) & \parallel \text{M}_{64:95} \\ \text{QRT}^3 \leftarrow {}^{32}(\text{M}_{96}) & \parallel \text{M}_{96:127} \\ \end{array}

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as 32-bit integers, sign extended to 64-bit integers, and placed into register QRT.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

### Quad-Vector Load Floating-point as Integer Word and Zero indeXed X-form

| qvlfiwzx  | QRT,RA,RB | (X=0) |

|-----------|-----------|-------|

| qvlfiwzxa | QRT,RA,RB | (X=1) |

| 31 | QRT | RA | RB | 839 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

The 16 bytes in storage addressed by the 16-byte-aligned EA are interpreted as 32-bit integers, zero extended to 64-bit integers, and placed into register QRT.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

### Quad-Vector Load Permute Control Left Double indeXed X-form

### qvlpcldx QRT,RA,RB

| 31 | QRT | RA | RB | 582 | /  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

A quad-vector (32 bytes) describing a dynamic double-precision data alignment to be performed using the quad-vector permute instruction *qvfperm* is generated based on the address EA.

The instruction may raise a memory translation exception if EA is not a valid address.

The behavior of this instruction is boundedly undefined when the address does not correspond to at least the natural alignment of an IEEE double precision floating point number.

### **Special Registers Altered:**

None

### **Programming Note**

This instruction allows the implementation of a software based alignment sequence for double-precision floating-point quad-vectors

```

qvlpcldx qalign, ra, rb

qvlfdux qmem1, ra, rb

qvlfdux qmem2, ra, rb

qvfperm qaligned, qmem1, qmem2, qalign

```

### Quad-Vector Load Permute Control Left Single indeXed X-form

qvlpclsx QRT,RA,RB

| 31 | QRT | RA | RB | 518 | /  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

A quad-vector (32 bytes) describing a dynamic single-precision data alignment to be performed using the quad-vector permute instruction *qvfperm* is generated based on the address EA.

The instruction may raise a memory translation exception if EA is not a valid address.

The behavior of this instruction is boundedly undefined when the address does not correspond to at least the natural alignment of an IEEE double precision floating point number.

### **Special Registers Altered:**

None

### Programming Note

This instruction allows the implementation of a software based alignment sequence for single-precision floating-point quad-vectors

```

qvlpclsxqalign, ra, rbqvlfsuxqmem1, ra, rbqvlfsuxqmem2, ra, rbqvfpermqaligned, qmem1, qmem2, qalign

```

# Quad-Vector Load Permute Control Right Double indeXed X-form

### qvlpcrdx QRT,RA,RB

| 31 | QRT | RA | RB | 70 | /  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

```

if RA = 0 then b \leftarrow 0

else

b \leftarrow (RA)

EA \leftarrow b + (RB)

AA = (32 - (EA \& 0b11000))

490

QRT<sup>0</sup> ← 0x400 ||

(AA )<sub>58:60</sub>

490

(AA+ 8)<sub>58:60</sub>

\mathtt{ORT}^1 \leftarrow

0x400

490

QRT<sup>2</sup> ←

(AA+16)<sub>58:60</sub>

0x400

490

0x400 || (AA+24)<sub>58:60</sub>

```

Let the effective address (EA) be the sum (RA|0)+(RB).

A quad-vector (32 bytes) describing a dynamic data alignment to be performed using the quad-vector permute instruction *qvfperm* is generated based on the address EA.

The instruction may raise a memory translation exception if EA is not a valid address.

The behavior of this instruction is boundedly undefined when the address does not correspond to at least the natural alignment of an IEEE double precision floating point number.

### **Special Registers Altered:**

None

### **Programming Note**

This instruction allows the implementation of a software based alignment sequence for double-precision floating-point quad-vectors.

### Quad-Vector Load Permute Control Right Single indeXed X-form

qvlpcrsx QRT,RA,RB

| 31 | QRT | RA | RB | 6  | /  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

A quad-vector (32 bytes) describing a dynamic data alignment to be performed using the quad-vector permute instruction *qvfperm* is generated based on the address EA.

The instruction may raise a memory translation exception if EA is not a valid address.

The behavior of this instruction is boundedly undefined when the address does not correspond to at least the natural alignment of an IEEE double precision floating point number.

### **Special Registers Altered:**

None

### **Programming Note**

This instruction allows the implementation of a software based alignment sequence for single-precision floating-point quad-vectors.

### 4.2 Quad-Vector Floating-Point Store Instructions

# Quad-Vector STore Floating-point Single indeXed X-form

| qvstfsx  | QRS,RA,RB | (X=0) |

|----------|-----------|-------|

| qvstfsxa | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 647 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

if RA = 0 then b \leftarrow 0 else b \leftarrow (RA) EA \leftarrow (b + (RB)) & 0xfFFFFFFFFFFFFFFFF 0 MEM(EA, 16) \leftarrowSINGLE(QRS^0) || SINGLE(QRS^1) || SINGLE(QRS^3)

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The four vector elements of register QRS are converted to single-precision format and stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

# Quad-Vector STore Floating-point Single with Update indeXed X-form

| qvstfsux  | QRS,RA,RB | (X=0) |

|-----------|-----------|-------|

| qvstfsuxa | QRS,RA,RB | (X=1) |

|   | 31 | QRS | RA | RB | 679 | Х  |

|---|----|-----|----|----|-----|----|

| 0 |    | 6   | 11 | 16 | 21  | 31 |

```

EA \leftarrow ((RA) + (RB)) & 0xFFFFFFFFFFFFF 0

MEM(EA, 16) \leftarrow SINGLE(QRS<sup>0</sup>) | | SINGLE(QRS<sup>1</sup>) | |

SINGLE(QRS<sup>2</sup>) | | SINGLE(QRS<sup>3</sup>)

```

Let the effective address (EA) be the sum (RA)+(RB).

The four vector elements of register QRS are converted to single-precision format and stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

#### **Special Registers Altered:**

## Quad-Vector STore Floating-point Single indeXed and Indicate X-form

| qvstfsxi  | QRS,RA,RB | (X=0) |

|-----------|-----------|-------|

| qvstfsxia | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 645 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

if RA = 0 then b \leftarrow 0

else

b \leftarrow (RA)

EA \leftarrow (b + (RB)) \& 0xFFFFFFFFFFFFFF

MEM(EA, 16) \leftarrow SINGLE(QRS^{0}) \mid | SINGLE(QRS^{1}) \mid |

SINGLE(QRS<sup>2</sup>) | SINGLE(QRS<sup>3</sup>)

if (SNEE = 1) then

if (isNaN (QRS<sup>0</sup>) OR

isNaN (QRS1) OR

isNaN (QRS2) OR

isNaN (QRS3)) then

ESR[AP] \leftarrow 1

if (SIEE = 1) then

if (isInf (QRS<sup>0</sup>) OR

isInf (QRS1) OR

isInf (QRS<sup>2</sup>) OR

isInf (QRS3)) then

ESR[AP] \leftarrow 1

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The four vector elements of register QRS are converted to single-precision format and stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### Special Registers Altered: ESR[AP]

# Quad-Vector STore Floating-point Single with Update indeXed and Indicate X-form

| qvstfsuxi  | QRS,RA,RB | (X=0) |

|------------|-----------|-------|

| qvstfsuxia | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 677 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{split} \text{EA} \leftarrow & ((\text{RA}) + (\text{RB})) \text{ & OxFFFFFFFFFFFF} \\ \text{MEM}(\text{EA}, 16) \leftarrow & \text{SINGLE}(\text{QRS}^0) \mid | \text{ SINGLE}(\text{QRS}^1) \mid | \\ & \text{SINGLE}(\text{QRS}^2) \mid | \text{ SINGLE}(\text{QRS}^3) \end{split} \text{RA} \leftarrow \text{EA} if (SNEE = 1) then if (isNaN (QRS^0) OR isNaN (QRS^1) OR isNaN (QRS^1) OR isNaN (QRS^2) OR isNaN (QRS^3)) then  \text{ESR}[\text{AP}] \leftarrow 1  if (SIEE = 1) then if (isInf (QRS^0) OR isInf (QRS^1) OR isInf (QRS^1) OR isInf (QRS^2) OR isInf (QRS^3)) then  \text{ESR}[\text{AP}] \leftarrow 1

```

Let the effective address (EA) be the sum (RA)+(RB).

The four vector elements of register QRS are converted to single-precision format and stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### Special Registers Altered:

ESR[AP]

# Quad-Vector STore Floating-point Double indeXed X-form

| qvstfdx  | QRS,RA,RB | (X=0 | )) |

|----------|-----------|------|----|

| qvstfdxa | QRS,RA,RB | (X=1 | )  |

| 31 | QRS | RA | RB | 711 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

The contents of register QRS are stored into the 32 bytes in storage addressed by the 32-byte-aligned EA.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

# Quad-Vector STore Floating-point Double with Update indeXed X-form

| qvstfdux  | QRS,RA,RB | (X=0) |

|-----------|-----------|-------|

| qvstfduxa | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 743 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

EA

$$\leftarrow$$

((RA) + (RB)) & 0xFFFFFFFFFFFE0 MEM(EA, 32)  $\leftarrow$  (QRS) RA  $\leftarrow$  EA

Let the effective address (EA) be the sum (RA)+(RB).

The contents of register QRS are stored into the 32 bytes in storage addressed by the 32-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

### **Special Registers Altered:**

#### **Quad-Vector STore Floating-point Double** indeXed and Indicate X-form

| qvstfdxi  | QRS,RA,RB | (X=0) |

|-----------|-----------|-------|

| qvstfdxia | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 709 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

if RA = 0 then b \leftarrow 0

else

b \leftarrow (RA)

EA \leftarrow (b + (RB)) \& 0xFFFFFFFFFFFE0

MEM(EA, 32) \leftarrow (QRS)

if (SNEE = 1) then

if (isNaN (QRS<sup>0</sup>) OR

isNaN (QRS<sup>1</sup>) OR

isNaN (QRS2) OR

isNaN (QRS3)) then

ESR[AP] \leftarrow 1

if (SIEE = 1) then

if (isInf (QRS<sup>0</sup>) OR

isInf (QRS<sup>1</sup>) OR

isInf (QRS<sup>2</sup>) OR

isInf (QRS<sup>3</sup>)) then

ESR[AP] \leftarrow 1

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The contents of register QRS are stored into the 32 bytes in storage addressed by the 32-byte-aligned EA.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

### **Special Registers Altered:** ESR[AP]

### **Quad-Vector STore Floating-point Double** with Update indeXed and Indicate X-form

| qvstfduxi  | QRS,RA,RB | (X=0) |

|------------|-----------|-------|

| qvstfduxia | QRS,RA,RB | (X=1) |

| 31 | QRS | RA | RB | 741 | Χ  |

|----|-----|----|----|-----|----|

| o  | 6   | 11 | 16 | 21  | 31 |

```

EA \leftarrow ((RA) + (RB)) \& 0xFFFFFFFFFFFE0

MEM(EA, 32) \leftarrow (QRS)

RA \leftarrow EA

if (SNEE = 1) then

if (isNaN (QRS<sup>0</sup>) OR

isNaN (QRS<sup>1</sup>) OR

isNaN (QRS<sup>2</sup>) OR

isNaN (QRS^3)) then

ESR[AP] \leftarrow 1

if (SIEE = 1) then

if (isInf (QRS<sup>0</sup>) OR

isInf (QRS<sup>1</sup>) OR

isInf (QRS<sup>2</sup>) OR

isInf(QRS^3)) then

ESR[AP] \leftarrow 1

```

Let the effective address (EA) be the sum (RA)+(RB).

The contents of register QRS are stored into the 32 bytes in storage addressed by the 32-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 32-byte boundary, an exception is raised.

### **Special Registers Altered:**

ESR[AP]

### Quad-Vector STore Floating-point Complex Single indeXed X-form

| qvstfcsx  | QRS,RA,RB | (X: | =0) |

|-----------|-----------|-----|-----|

| qvstfcsxa | QRS,RA,RB | (X: | =1) |

| 31 | QRS | RA | RB | 135 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

Vector elements 0 and 1 of register QRS are converted to single-precision format and stored into the 8 bytes in storage addressed by the 8-byte-aligned EA.

If the X bit is set, and the address is not aligned on an 8-byte boundary, an exception is raised.

#### **Special Registers Altered:**

None

### Quad-Vector STore Floating-point Complex Double indeXed X-form

qvstfcdx QRS,RA,RB (X=0) qvstfcdxa QRS,RA,RB (X=1)

| 31 | QRS | RA | RB | 199 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

Vector elements 0 and 1 of register QRS are stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

#### **Special Registers Altered:**

### Quad-Vector STore Floating-point Complex Single indeXed and Indicate X-form

qvstfcsxi QRS,RA,RB (X=0) qvstfcsxia QRS,RA,RB (X=1)

| 31 | QRS | RA | RB | 133 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

if RA = 0 then b \leftarrow 0 else b \leftarrow (RA) EA \leftarrow (b + (RB)) & 0xFFFFFFFFFFFFF8 MEM(EA, 8) \leftarrow SINGLE(QRS<sup>0</sup>) || SINGLE(QRS<sup>1</sup>) if (SNEE = 1) then if (isNaN (QRS<sup>0</sup>) OR isNaN (QRS<sup>1</sup>)) then ESR[AP] \leftarrow 1 if (SIEE = 1) then if (isInf (QRS<sup>0</sup>) OR isInf (QRS<sup>1</sup>)) then ESR[AP] \leftarrow 1

```

Let the effective address (EA) be the sum (RA|0)+(RB).

Vector elements 0 and 1 of register QRS are converted to single-precision format and stored into the 8 bytes in storage addressed by the 8-byte-aligned EA.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on an 8-byte boundary, an exception is raised.

### **Special Registers Altered:**

ESR[AP]

### Quad-Vector STore Floating-point Complex Double indeXed and Indicate X-form

qvstfcdxi QRS,RA,RB (X=0) qvstfcdxia QRS,RA,RB (X=1)

| 31 | QRS | RA | RB | 197 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

Vector elements 0 and 1 of register QRS are stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### Special Registers Altered:

ESR[AP]

### Quad-Vector STore Floating-point Complex Single with Update indeXed X-form

$\begin{array}{lll} \text{qvstfcsux} & \text{QRS,RA,RB} & \text{(X=0)} \\ \text{qvstfcsuxa} & \text{QRS,RA,RB} & \text{(X=1)} \\ \end{array}$

| 31 | QRS | RA | RB | 167 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

$$\begin{array}{lll} \texttt{EA} \leftarrow ((\texttt{RA}) + (\texttt{RB})) \& \texttt{0xffffffffffffff} \\ \texttt{MEM}(\texttt{EA}, \texttt{8}) \leftarrow \texttt{SINGLE}(\texttt{QRS}^0) \mid \mid \texttt{SINGLE}(\texttt{QRS}^1) \\ \texttt{RA} \leftarrow \texttt{EA} \end{array}$$

Let the effective address (EA) be the sum (RA)+(RB).

Vector elements 0 and 1 of register QRS are converted to single-precision format and stored into the 8 bytes in storage addressed by the 8-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on an 8-byte boundary, an exception is raised.

### **Special Registers Altered:**

None

### Quad-Vector STore Floating-point Complex Double with Update indeXed X-form

$\begin{array}{lll} \mbox{qvstfcdux} & \mbox{QRS,RA,RB} & (\mbox{X=0}) \\ \mbox{qvstfcduxa} & \mbox{QRS,RA,RB} & (\mbox{X=1}) \end{array}$

| 31 | QRS | RA | RB | 231 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

EA

$$\leftarrow$$

((RA) + (RB)) & 0xFFFFFFFFFFFF 0 MEM(EA, 16)  $\leftarrow$  QRS 0 || QRS 1 RA  $\leftarrow$  EA

Let the effective address (EA) be the sum (RA)+(RB).

Vector elements 0 and 1 of register QRS are stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

### Quad-Vector STore Floating-point Complex Single with Update indeXed and Indicate X-form

qvstfcsuxi QRS,RA,RB (X=0) qvstfcsuxia QRS,RA,RB (X=1)

| 31 | QRS | RA | RB | 165 | Х  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{split} \text{EA} &\leftarrow ((\text{RA}) + (\text{RB})) \& \text{ 0xFFFFFFFFFFF8} \\ \text{MEM}(\text{EA}, 8) &\leftarrow \text{SINGLE}(\text{QRS}^0) \mid \mid \text{SINGLE}(\text{QRS}^1) \\ \text{RA} &\leftarrow \text{EA} \end{split} if (SNEE = 1) then if (isNaN (QRS^0) OR isNaN (QRS^1)) then  &\text{ESR}[\text{AP}] \leftarrow 1 \\ \text{if (SIEE = 1) then} \\ \text{if (isInf (QRS^0) OR} \\ \text{isInf (QRS^1)) then} \\ &\text{ESR}[\text{AP}] \leftarrow 1 \end{split}

```

Let the effective address (EA) be the sum (RA)+(RB).

Vector elements 0 and 1 of register QRS are converted to single-precision format and stored into the 8 bytes in storage addressed by the 8-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on an 8-byte boundary, an exception is raised.

### **Special Registers Altered:**

ESR[AP]

### Quad-Vector STore Floating-point Complex Double with Update indeXed and Indicate X-form

qvstfcduxi QRS,RA,RB (X=0) qvstfcduxia QRS,RA,RB (X=1)

| 31 | QRS | RA | RB | 229 | Χ  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{split} \text{EA} &\leftarrow (\text{(RA)} + \text{(RB)}) &\& \text{ OxFFFFFFFFFFF0} \\ \text{MEM(EA, 16)} &\leftarrow \text{QRS}^0 \parallel \text{QRS}^1 \\ \text{RA} &\leftarrow \text{EA} \end{split} if (SNEE = 1) then if (isNaN (QRS^0) OR isNaN (QRS^1)) then \text{ESR[AP]} \leftarrow 1 if (SIEE = 1) then if (isInf (QRS^0) OR isInf (QRS^1)) then \text{ESR[AP]} \leftarrow 1

```

Let the effective address (EA) be the sum (RA)+(RB).

Vector elements 0 and 1 of register QRS are stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

EA is placed into register RA.

If RA=0, the instruction form is invalid.

If any vector element being stored is a NaN (or Infinity), and the corresponding Store NaN (or Infinity) Exception is enabled, then the Auxiliary Processor bit of the Exception Syndrome Register (ESR[AP]) is set.

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

ESR[AP]

### Quad-Vector STore Floating-point as Integer Word indeXed X-form

| qvstfiwx  | QRS,RA,RB | () | X=0) |

|-----------|-----------|----|------|

| qvstfiwxa | QRS,RA,RB | () | X=1) |

| 31 | QRS | RA | RB | 967 | X  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

```

\begin{array}{lll} \text{if RA = 0 then b} \leftarrow 0 \\ \text{else} & \text{b} \leftarrow \text{(RA)} \\ \text{EA} \leftarrow \text{(b + (RB))} \& 0 \\ \text{XFFFFFFFFFFFFFFFFM} \\ \text{MEM(EA, 16)} \leftarrow & Q \\ \text{RS}^0_{32:63} & || & Q \\ \text{RS}^3_{32:63} & || & Q \\ \text{RS}^3_{32:63} & || & Q \\ \end{array}

```

Let the effective address (EA) be the sum (RA|0)+(RB).

The least significant 32 bits of each vector element of register QRS are stored into the 16 bytes in storage addressed by the 16-byte-aligned EA.

If the contents of register QRS were produced, either directly or indirectly, by a Load Floating-Point Single instruction, a single-precision Arithmetic instruction, or frsp, then the value stored is undefined. (The contents of register QRS are produced directly by such an instruction if QRS is the target register for the instruction. The contents of register QRS are produced indirectly by such an instruction if QRS is the final target register of a sequence of one or more Floating-Point Move instructions, with the input to the sequence having been produced directly by such an instruction.)

If the X bit is set, and the address is not aligned on a 16-byte boundary, an exception is raised.

### **Special Registers Altered:**

### 4.3 Quad-Vector Floating-Point Move Instructions

# Quad-Vector Floating-point Move Register X-form

qvfmr QRT,QRB

| 4 | QRT | /// | QRB | 72 | /  |

|---|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21 | 31 |

For each vector element, the contents of register QRB are placed into register QRT.

### **Special Registers Altered:**

None

## Quad-Vector Floating-point NEGate X-form

qvfneg QRT,QRB

| ſ | 4 | QRT | /// | QRB | 40 | /  |

|---|---|-----|-----|-----|----|----|

| ( | ) | 6   | 11  | 16  | 21 | 31 |

For each vector element, the contents of register QRB, with bit 0 inverted, are placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point ABSolute value X-form

qvfabs QRT,QRB

|   | 4 | ORT | /// | QRB   | 264 | /   |

|---|---|-----|-----|-------|-----|-----|

|   | • | σ   | ""  | Q. LD |     | l ′ |

| О |   | 6   | 11  | 16    | 21  | 31  |

For each vector element, the contents of register QRB, with bit 0 set to zero, are placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Negative ABSolute value X-form

qvfnabs QRT,QRB

| _  |   |       |     |       |     |     |

|----|---|-------|-----|-------|-----|-----|

| 1  | 4 | ORT   | /// | ORB   | 136 | /   |

|    | • | Q. C. | ""  | Q. LD | .00 | l ′ |

| n  |   | 6     | 11  | 16    | 21  | 31  |

| I۳ |   | J~    | 1   | 1.0   | F ' | ١٠. |

For each vector element, the contents of register QRB, with bit 0 set to one, are placed into register QRT.

### **Special Registers Altered:**

None

## Quad-Vector Floating-point CoPy SiGN X-form

qvfcpsgn QRT,QRA,QRB

| 4 | QRT | QRA | QRB | 8  | /  |

|---|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21 | 31 |

$\begin{array}{llll} \text{QRT}_0 & \leftarrow & \text{QRA}_0 \\ \text{QRT}_{1:63} & \leftarrow & \text{QRB}_{1:63} \\ \text{QRT}_{64} & \leftarrow & \text{QRA}_{64} \\ \text{QRT}_{65:127} & \leftarrow & \text{QRB}_{65:127} \\ \text{QRT}_{128} & \leftarrow & \text{QRA}_{128} \\ \text{QRT}_{129:191} & \leftarrow & \text{QRB}_{129:191} \\ \text{QRT}_{192} & \leftarrow & \text{QRA}_{192} \\ \text{QRT}_{193:255} & \leftarrow & \text{QRB}_{193:255} \end{array}$

For each vector element, the contents of register QRB, with bit 0 set to the value of bit 0 of register QRA, are placed into register QRT.

### **Special Registers Altered:**

### 4.4 Quad-Vector Floating-Point Arithmetic Instructions

### 4.4.1 Quad-Vector Floating-Point Elementary Arithmetic Instructions

### Quad-Vector Floating-point ADD [Single] A-form

# qvfadd QRT,QRA,QRB 4 QRT QRA QRB /// 21 / 0 6 11 16 21 26 31

| qvfadds | QR1, | QRA,QR | B |  |

|---------|------|--------|---|--|

|         |      |        |   |  |

|         |      |        |   |  |

| 0 | QRT | QRA | QRB | /// | 21 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

For each vector element, the floating-point operand in register QRA is added to the floating-point operand in register QRB.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

Floating-point addition is based on exponent comparison and addition of the two significands. The exponents of the two operands are compared, and the significand accompanying the smaller exponent is shifted right, with its exponent increased by one for each bit shifted, until the two exponents are equal. The two significands are then added or subtracted as appropriate, depending on the signs of the operands, to form an intermediate sum. All 53 bits of the significand as well as all three guard bits (G, R, and X) enter into the computation

If a carry occurs, the sum's significand is shifted right one bit position and the exponent is increased by one.

#### **Special Registers Altered:**

None

# Quad-Vector Floating-point SUBtract [Single] A-form

| qvfsub  | QRT, | QRA,QR | RB  |     |    |    |

|---------|------|--------|-----|-----|----|----|

| 4       | QRT  | QRA    | QRB | /// | 20 | /  |

| 0       | 6    | 11     | 16  | 21  | 26 | 31 |

| qvfsubs | QRT, | QRA,QR | RB  |     |    |    |

| 0       | QRT  | QRA    | QRB | /// | 20 | /  |

For each vector element, the floating-point operand in register QRB is subtracted from the floating-point operand in register QRA.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

The execution of the Floating Subtract instruction is identical to that of Floating Add, except that the contents of QRB participate in the operation with the sign bit (bit 0) inverted.

### **Special Registers Altered:**

### Quad-Vector Floating-point MULtiply [Single] A-form

### qvfmul QRT,QRA,QRC

| 4 | QRT | QRA | /// | QRC | 25 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

#### qvfmuls QRT,QRA,QRC

| 0 | QRT | QRA | /// | QRC | 25 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

For each vector element, the floating-point operand in register QRA is multiplied by the floating-point operand in register QRC.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

Floating-point multiplication is based on exponent addition and multiplication of the significands.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Reciprocal Estimate [Single] A-form

qvfre QRT,QRB

| 4 | QRT | /// | QRB | /// | 24 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfres QRT,QRB

| 0 | QRT | /// | QRB | /// | 24 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

For each vector element, an estimate of the reciprocal of the floating-point operand in register QRB is placed into register QRT. The estimate placed into register QRT is correct to a precision of one part in 16384 of the reciprocal of (QRB), i.e.,

$$ABS(\frac{estimate - 1/x}{1/x}) \le \frac{1}{16384}$$

where x is the initial value in QRB.

Operation with various special values of the operand is summarized below.

| Result |

|--------|

| -0     |

| -∞     |

| +∞     |

| +0     |

| QNaN   |

| QNaN   |

|        |

The results of executing this instruction may vary between implementations.

### **Special Registers Altered:**

# Quad-Vector Floating-point Reciprocal SQuare RooT Estimate [Single] A-form

qvfrsqrte QRT,QRB

| 4 | QRT | /// | QRB | /// | 26 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfrsqrtes QRT,QRB

| 0 | QRT | /// | QRB | /// | 26 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

For each vector element, an estimate of the reciprocal of the square root of the floating-point operand in register QRB is placed into register QRT. The estimate placed into register QRT is correct to a precision of one part in 16384 of the reciprocal of the square root of (QRB), i.e.,

$$ABS(\frac{estimate - 1/(\sqrt{x})}{1/(\sqrt{x})}) \le \frac{1}{16384}$$

where x is the initial value in QRB.

Operation with various special values of the operand is summarized below.

| Operand | Result |

|---------|--------|

| -∞      | QNaN   |

| < 0     | QNaN   |

| -0      | -∞     |

| +0      | +∞     |

| +∞      | +0     |

| SNaN    | QNaN   |

| QNaN    | QNaN   |

The results of executing this instruction may vary between implementations.

### **Special Registers Altered:**

### 4.4.2 Quad-Vector Floating-Point Multiply-Add Instructions

# Quad-Vector Floating-point Multiply-ADD [Single] A-form

### qvfmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 29 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

### qvfmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 29 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

### The operations

```

\begin{array}{l} \text{QRT}^0 \leftarrow [(\text{QRA}^0) \times (\text{QRC}^0)] + (\text{QRB}^0) \\ \text{QRT}^1 \leftarrow [(\text{QRA}^1) \times (\text{QRC}^1)] + (\text{QRB}^1) \\ \text{QRT}^2 \leftarrow [(\text{QRA}^2) \times (\text{QRC}^2)] + (\text{QRB}^2) \\ \text{QRT}^3 \leftarrow [(\text{QRA}^3) \times (\text{QRC}^3)] + (\text{QRB}^3) \end{array}

```

are performed.

For each vector element, the floating-point operand in register QRA is multiplied by the floating-point operand in register QRC. The floating-point operand in register QRB is added to this intermediate result.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Multiply-SUBtract [Single]

A-form

| qvfmsub | QRT,QRA,QRC,QRB |

|---------|-----------------|

|---------|-----------------|

| 4 | QRT | QRA | QRB | QRC | 28 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

### qvfmsubs QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 28 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

### The operations

$$\begin{array}{l} \text{QRT}^0 \leftarrow [(\text{QRA}^0) \times (\text{QRC}^0)] - (\text{QRB}^0) \\ \text{QRT}^1 \leftarrow [(\text{QRA}^1) \times (\text{QRC}^1)] - (\text{QRB}^1) \\ \text{QRT}^2 \leftarrow [(\text{QRA}^2) \times (\text{QRC}^2)] - (\text{QRB}^2) \\ \text{QRT}^3 \leftarrow [(\text{QRA}^3) \times (\text{QRC}^3)] - (\text{QRB}^3) \end{array}$$

are performed.

For each vector element, the floating-point operand in register QRA is multiplied by the floating-point operand in register QRC. The floating-point operand in register QRB is subtracted from this intermediate result.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

### Quad-Vector Floating-point Negative Multiply-ADD [Single] A-form

qvfnmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 31 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfnmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 31 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

#### The operations

```

\begin{array}{l} {\sf QRT^0} \leftarrow - \; (\; [({\sf QRA^0}) \times ({\sf QRC^0})] \; + \; ({\sf QRB^0}) \; ) \\ {\sf QRT^1} \leftarrow - \; (\; [({\sf QRA^1}) \times ({\sf QRC^1})] \; + \; ({\sf QRB^1}) \; ) \\ {\sf QRT^2} \leftarrow - \; (\; [({\sf QRA^2}) \times ({\sf QRC^2})] \; + \; ({\sf QRB^2}) \; ) \\ {\sf QRT^3} \leftarrow - \; (\; [({\sf QRA^3}) \times ({\sf QRC^3})] \; + \; ({\sf QRB^3}) \; ) \end{array}

```

are performed.

For each vector element, the floating-point operand in register QRA is multiplied by the floating-point operand in register QRC. The floating-point operand in register QRB is added to this intermediate result.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, then negated and placed into register QRT.

This instruction produces the same result as would be obtained by using the *qvfmadd* instruction and then negating the result, with the following exceptions.

QNaNs propagate with no effect on their "sign" bit. QNaNs that are generated as the result of a disabled Invalid Operation Exception have a "sign" bit of 0.

SNaNs that are converted to QNaNs as the result of a disabled Invalid Operation Exception retain the "sign" bit of the SNaN.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Negative Multiply-SUBtract [Single] A-form

qvfnmsub QRT,QRA,QRC,QRB

| Ī | 4 | QRT | QRA | QRB | QRC | 30 | /  |

|---|---|-----|-----|-----|-----|----|----|

|   | 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfnmsubs QRT,QRA,QRC,QRB

| Γ | 0 | QRT | QRA | QRB | QRC | 30 | /  |

|---|---|-----|-----|-----|-----|----|----|

| ( | ) | 6   | 11  | 16  | 21  | 26 | 31 |

#### The operations

```

QRT^{0} \leftarrow - ([(QRA^{0}) \times (QRC^{0})] - (QRB^{0}))

QRT^{1} \leftarrow - ([(QRA^{1}) \times (QRC^{1})] - (QRB^{1}))

QRT^{2} \leftarrow - ([(QRA^{2}) \times (QRC^{2})] - (QRB^{2}))

QRT^{3} \leftarrow - ([(QRA^{3}) \times (QRC^{3})] - (QRB^{3}))

```

are performed.

For each vector element, the floating-point operand in register QRA is multiplied by the floating-point operand in register QRC. The floating-point operand in register QRB is subtracted from this intermediate result.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, then negated and placed into register QRT.

This instruction produces the same result as would be obtained by using the *qvfmsub* instruction and then negating the result, with the following exceptions.

QNaNs propagate with no effect on their "sign" bit. QNaNs that are generated as the result of a disabled Invalid Operation Exception have a "sign" bit of 0.

SNaNs that are converted to QNaNs as the result of a disabled Invalid Operation Exception retain the "sign" bit of the SNaN.

### **Special Registers Altered:**

# Quad-Vector Floating-point cross (X) Multiply-ADD [Single] A-form

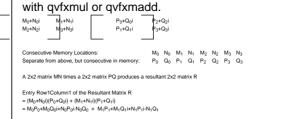

qvfxmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 9  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfxmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 9  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

The operations

$$\begin{array}{l} \text{QRT}^0 \leftarrow [(\text{QRA}^0) \times (\text{QRC}^0)] + (\text{QRB}^0) \\ \text{QRT}^1 \leftarrow [(\text{QRA}^0) \times (\text{QRC}^1)] + (\text{QRB}^1) \\ \text{QRT}^2 \leftarrow [(\text{QRA}^2) \times (\text{QRC}^2)] + (\text{QRB}^2) \\ \text{QRT}^3 \leftarrow [(\text{QRA}^2) \times (\text{QRC}^3)] + (\text{QRB}^3) \end{array}$$

are performed.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

None

### Programming Note -

This instruction is typically used in cross-product multiplication, and in conjunction with qvfxxnp-madd.

# Quad-Vector Floating-point double-cross complex (XXNP) Multiply-ADD [Single] A-form

qvfxxnpmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 11 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfxxnpmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 11 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

The operations

$$\begin{array}{lll} & \text{QRT}^0 \leftarrow - \ ( \ [(\text{QRA}^1) \times (\text{QRC}^1)] - (\text{QRB}^0) \ ) \\ & \text{QRT}^1 \leftarrow & [(\text{QRA}^0) \times (\text{QRC}^1)] + (\text{QRB}^1) \\ & \text{QRT}^2 \leftarrow - \ ( \ [(\text{QRA}^3) \times (\text{QRC}^3)] - (\text{QRB}^2) \ ) \\ & \text{QRT}^3 \leftarrow & [(\text{QRA}^2) \times (\text{QRC}^3)] + (\text{QRB}^3) \end{array}$$

are performed.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR. For vector elements 0 and 2, the rounded result is negated and placed into register QRT. For vector elements 1 and 3, the rounded result is placed into register QRT.

### **Special Registers Altered:**

None

#### **Programming Note**

This instruction is typically used in cross-product multiplication of complex numbers, in conjunction with gyfxmul or gyfxmadd.

|       | Element <sup>0</sup> | Element <sup>1</sup> | Element <sup>2</sup> | Element <sup>3</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|

| QPR20 | M <sub>O</sub>       | N <sub>0</sub>       | M <sub>1</sub>       | N <sub>1</sub>       |

|       |                      |                      |                      |                      |

|       | - 0                  | - 1                  |                      |                      |

|       | Element <sup>0</sup> | Element <sup>1</sup> | Element <sup>2</sup> | Element <sup>3</sup> |

qvfxmul QPR22, QPR20, QPR21 (notice A=QPR20 and C=QPR21) yields:

|       | Element <sup>0</sup>          | Element <sup>1</sup> | Element <sup>2</sup>          | Element <sup>3</sup>          |

|-------|-------------------------------|----------------------|-------------------------------|-------------------------------|

| QPR22 | M <sub>0</sub> P <sub>0</sub> | $M_0Q_0$             | M <sub>1</sub> P <sub>1</sub> | M <sub>1</sub> Q <sub>1</sub> |

qvfxxnpmadd QPR23, QPR21, QPR20, QPR22 (notice A=QPR21 and C=QPR20) yields:

|                    | Element                                                       | Element'           | Element <sup>2</sup>                                          | Element                                                       |

|--------------------|---------------------------------------------------------------|--------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| QPR23              | M <sub>0</sub> P <sub>0</sub> - N <sub>0</sub> Q <sub>0</sub> | $M_0Q_0 + N_0P_0$  | M <sub>1</sub> P <sub>1</sub> - N <sub>1</sub> Q <sub>1</sub> | M <sub>1</sub> Q <sub>1</sub> + N <sub>1</sub> P <sub>1</sub> |

| Now pood to odd El | omant <sup>0</sup> : Elamant <sup>2</sup> on                  | d Element L Elemen | <sub>•</sub> 3                                                |                                                               |

low need to add Element<sup>0</sup>+Element<sup>2</sup> and Element<sup>1</sup>+Element<sup>3</sup>

# Quad-Vector Floating-point double-cross conjugate (XXCPN) Multiply-ADD [Single] A-form

qvfxxcpnmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 3  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfxxcpnmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 3  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

The operations

$$\begin{array}{lll} \text{QRT}^0 \leftarrow & [(\text{QRA}^1) \times (\text{QRC}^1)] + (\text{QRB}^0) \\ \text{QRT}^1 \leftarrow - \left( & [(\text{QRA}^0) \times (\text{QRC}^1)] - (\text{QRB}^1) \right) \\ \text{QRT}^2 \leftarrow & [(\text{QRA}^3) \times (\text{QRC}^3)] + (\text{QRB}^2) \\ \text{QRT}^3 \leftarrow - \left( & [(\text{QRA}^2) \times (\text{QRC}^3)] - (\text{QRB}^3) \right) \end{array}$$

are performed.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR. For vector elements 0 and 2, the rounded result is placed into register QRT. For vector elements 1 and 3, the rounded result is negated and placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point double-cross (XX) Multiply-ADD [Single] A-form

qvfxxmadd QRT,QRA,QRC,QRB

| 4 | QRT | QRA | QRB | QRC | 1  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfxxmadds QRT,QRA,QRC,QRB

| 0 | QRT | QRA | QRB | QRC | 1  | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

The operations

$$\begin{array}{l} \mathsf{QRT}^0 \leftarrow [(\mathsf{QRA}^1) \times (\mathsf{QRC}^1)] + (\mathsf{QRB}^0) \\ \mathsf{QRT}^1 \leftarrow [(\mathsf{QRA}^0) \times (\mathsf{QRC}^1)] + (\mathsf{QRB}^1) \\ \mathsf{QRT}^2 \leftarrow [(\mathsf{QRA}^3) \times (\mathsf{QRC}^3)] + (\mathsf{QRB}^2) \\ \mathsf{QRT}^3 \leftarrow [(\mathsf{QRA}^2) \times (\mathsf{QRC}^3)] + (\mathsf{QRB}^3) \end{array}$$

are performed.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

### Quad-Vector Floating-point cross (X) MULtiply [Single] A-1 A-form

qvfxmul QRT,QRA,QRC

| 4 | QRT | QRA | /// | QRC | 17 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

qvfxmuls QRT,QRA,QRC

| 0 | QRT | QRA | /// | QRC | 17 | /  |

|---|-----|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21  | 26 | 31 |

The operations

QRT<sup>0</sup>  $\leftarrow$  (QRA<sup>0</sup>)  $\times$  (QRC<sup>0</sup>) QRT<sup>1</sup>  $\leftarrow$  (QRA<sup>0</sup>)  $\times$  (QRC<sup>1</sup>) QRT<sup>2</sup>  $\leftarrow$  (QRA<sup>2</sup>)  $\times$  (QRC<sup>2</sup>)

$QRT^3 \leftarrow (QRA^2) \times (QRC^3)$

are performed.

For each vector element, the resultant significand may require normalization or denormalization, depending on the values of the two most significant bits of the resultant significand and on the value of the resultant exponent. The result is rounded to the target precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

# 4.5 Quad-Vector Floating-Point Rounding and Conversion Instructions

### 4.5.1 Quad-Vector Floating-Point Rounding Instruction

# Quad-Vector Floating-point Round to Single-Precision X-form

| qvfrsp | QRT, | QRB |     |    |    |

|--------|------|-----|-----|----|----|

| 4      | QRT  | /// | QRB | 12 | /  |

| 0      | 6    | 11  | 16  | 21 | 31 |

For each vector element, the floating-point operand in register QRB is rounded to single-precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

### 4.5.2 Quad-Vector Floating-Point Convert To/From Integer Instructions

### Quad-Vector Floating-point Convert To Integer Doubleword X-form

qvfctid QRT,QRB

| 4 | QRT | /// | QRB | 814 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer under control of the Floating-Point Rounding Control field (RN) of the FPSCR.

For each vector element, if the rounded floating-point integer is greater than  $2^{63}$  – 1, then QRT is set to  $0 \times 7 \text{FFF}\_\text{FFFF}\_\text{FFFF}\_\text{FFFF}$ .

For each vector element, if the rounded floating-point integer is less than  $-2^{63}$ , then QRT is set to  $0x8000\_0000\_0000\_0000$ .

Otherwise, for each vector element, QRT is set to the value of the rounded floating-point integer converted to 64-bit signed-integer format.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Convert To Integer Doubleword Unsigned X-form

qvfctidu QRT,QRB

|   | 4 | ORT      | /// | ORR    | 942  | 1     |

|---|---|----------|-----|--------|------|-------|

|   | 7 | GIV.     | /// | Q I LD | J 72 | ١′    |

|   |   | 6        | 11  | 16     | 21   | 21    |

| U |   | lo<br>lo |     | 110    | 2    | J J I |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer under control of the Floating-Point Rounding Control field (RN) of the FPSCR.

For each vector element, if the rounded floating-point integer is greater than  $2^{64}$  – 1, then QRT is set to 0xFFFF FFFF FFFF FFFF.

For each vector element, if the rounded floating-point integer is less than 0.0, then QRT is set to  $0 \times 0000\_0000\_0000\_0000$ .

Otherwise, for each vector element, QRT is set to the value of the rounded floating-point integer converted to 64-bit unsigned-integer format.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Convert To Integer Doubleword with round toward Zero X-form

qvfctidz QRT,QRB

| 4 | QRT | /// | QRB | 815 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward Zero.

For each vector element, if the rounded floating-point integer is greater than  $2^{63}$  – 1, then QRT is set to 0x7FFF FFFF FFFF FFFF.

For each vector element, if the rounded floating-point integer is less than  $-2^{63}$ , then QRT is set to  $0x8000_0000_0000_0000$ .

Otherwise, for each vector element, QRT is set to the value of the rounded floating-point integer converted to 64-bit signed-integer format.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Convert To Integer Doubleword Unsigned with round toward Zero X-form

qvfctiduz QRT,QRB

|   | 4 | QRT | /// | QRB | 943 | /  |

|---|---|-----|-----|-----|-----|----|

| 0 |   | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward Zero.

For each vector element, if the rounded floating-point integer is greater than  $2^{64}$  – 1, then QRT is set to 0xFFFF FFFF FFFF.

For each vector element, if the rounded floating-point integer is less than 0.0, then QRT is set to  $0 \times 0000\_0000\_0000\_0000$ .

Otherwise, for each vector element, QRT is set to the value of the rounded floating-point integer converted to 64-bit unsigned-integer format.

### **Special Registers Altered:**

### Quad-Vector Floating-point Convert To Integer Word X-form

qvfctiw QRT,QRB

| 4 | QRT | /// | QRB | 14 | /  |

|---|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21 | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer under control of the Floating-Point Rounding Control field (RN) of the FPSCR.

For each vector element, if the rounded floating-point integer is greater than  $2^{31}$  – 1, then QRT<sub>32:63</sub> is set to 0x7FFF FFFF.

For each vector element, if the rounded floating-point integer is less than  $-2^{31}$ , then QRT<sub>32:63</sub> is set to  $0x8000\_0000$ .

Otherwise, for each vector element, QRT<sub>32:63</sub> is set to the value of the rounded floating-point integer converted to 32-bit signed-integer format.

QRT<sub>0:31</sub> of each vector element is undefined.

#### **Special Registers Altered:**

None

### **Implementation Note**

In the QPU of BGQ, for each vector element,  $\text{QRT}_{0:31} \leftarrow \text{0x7FF80000}$

### Quad-Vector Floating-point Convert To Integer Word Unsigned X-form

qvfctiwu QRT,QRB

| 4 | QRT | /// | QRB | 142 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer under control of the Floating-Point Rounding Control field (RN) of the FPSCR.

For each vector element, if the rounded floating-point integer is greater than  $2^{32}$  – 1, then QRT<sub>32:63</sub> is set to 0xFFFF FFFF.

For each vector element, if the rounded floating-point integer is less than 0.0, then QRT $_{32:63}$  is set to  $0 \times 0000 - 0000$ .

Otherwise, for each vector element, QRT<sub>32:63</sub> is set to the value of the rounded floating-point integer converted to 32-bit unsigned-integer format.

QRT<sub>0:31</sub> of each vector element is undefined.

#### **Special Registers Altered:**

None

### Implementation Note

In the QPU of BGQ, for each vector element,  $\text{QRT}_{0:31} \leftarrow \text{0x7FF80000}$

### Quad-Vector Floating-point Convert To Integer Word with round toward Zero X-form

qvfctiwz QRT,QRB

| 4 | QRT | /// | QRB | 15 | /  |

|---|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21 | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward Zero.

For each vector element, if the rounded floating-point integer is greater than  $2^{31}$  – 1, then QRT<sub>32:63</sub> is set to  $0 \times 7 \text{FFF}\_\text{FFFF}$ .

For each vector element, if the rounded floating-point integer is less than  $-2^{31}$ , then QRT<sub>32:63</sub> is set to  $0 \times 8000\_0000$ .

Otherwise, for each vector element, QRT<sub>32:63</sub> is set to the value of the rounded floating-point integer converted to 32-bit signed-integer format.

QRT<sub>0:31</sub> of each vector element is undefined.

### **Special Registers Altered:**

None

#### Implementation Note

In the QPU of BGQ, for each vector element,  $\text{QRT}_{0:31} \leftarrow 0 \text{x7FF80000}$

### Quad-Vector Floating-point Convert To Integer Word Unsigned with round toward Zero X-form

qvfctiwuz QRT,QRB

| 4 | QRT | /// | QRB | 143 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward Zero.

For each vector element, if the rounded floating-point integer is greater than  $2^{32}$  – 1, then QRT<sub>32:63</sub> is set to  $0xFFFF_FFFFF$ .

For each vector element, if the rounded floating-point integer is less than 0.0, then QRT $_{32:63}$  is set to  $0x0000_0000$ .

Otherwise, for each vector element, QRT<sub>32:63</sub> is set to the value of the rounded floating-point integer converted to 32-bit unsigned-integer format.

QRT<sub>0:31</sub> of each vector element is undefined.

### **Special Registers Altered:**

None

#### Implementation Note

In the QPU of BGQ, for each vector element,  $\text{QRT}_{0:31} \leftarrow \text{0x7FF80000}$

# Quad-Vector Floating-point Convert From Integer Doubleword X-form

qvfcfid QRT,QRB

| 4 | QRT | /// | QRB | 846 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the 64-bit signed fixed-point operand in register QRB is converted to an infinitely precise floating-point integer. The result of the conversion is rounded to double-precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Convert From Integer Doubleword Unsigned X-form

qvfcfidu QRT,QRB

| 4 | QRT | /// | QRB | 974 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the 64-bit unsigned fixed-point operand in register QRB is converted to an infinitely precise floating-point integer. The result of the conversion is rounded to double-precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Convert From Integer Doubleword Single X-form

qvfcfids QRT,QRB

| 0 | QRT | /// | QRB | 846 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the 64-bit signed fixed-point operand in register QRB is converted to an infinitely precise floating-point integer. The result of the conversion is rounded to single-precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Convert From Integer Doubleword Unsigned Single X-form

qvfcfidus QRT,QRB

| 0 | QRT | /// | QRB | 974 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the 64-bit unsigned fixed-point operand in register QRB is converted to an infinitely precise floating-point integer. The result of the conversion is rounded to single-precision under control of the Floating-Point Rounding Control field (RN) of the FPSCR, and placed into register QRT.

### **Special Registers Altered:**

### 4.5.3 Quad-Vector Floating-Point Round to Integer Instructions

# Quad-Vector Floating-point Round to Integer Nearest X-form

qvfrin QRT,QRB

| ĺ | 4 | QRT | /// | QRB | 392 | /  |

|---|---|-----|-----|-----|-----|----|

|   | 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer as follows, with the result placed into register QRT. If the sign of the operand is positive, (QRB) + 0.5 is truncated to a floating-point integer, otherwise (QRB) - 0.5 is truncated to a floating-point integer.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Round to Integer Plus X-form

qvfrip QRT,QRB

|   | 4 | QRT | /// | QRB | 456 | /  |

|---|---|-----|-----|-----|-----|----|

| 0 |   | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward +Infinity, and the result is placed into register QRT.

### **Special Registers Altered:**

None

### Quad-Vector Floating-point Round to Integer toward Zero X-form

qvfriz QRT,QRB

| 4 | QRT | /// | QRB | 424 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward Zero, and the result is placed into register QRT.

### **Special Registers Altered:**

None

# Quad-Vector Floating-point Round to Integer Minus X-form

qvfrim QRT,QRB

| 4 | QRT | /// | QRB | 488 | /  |

|---|-----|-----|-----|-----|----|

| 0 | 6   | 11  | 16  | 21  | 31 |

For each vector element, the floating-point operand in register QRB is rounded to a floating-point integer using the rounding mode Round toward -Infinity, and the result is placed into register QRT.

### **Special Registers Altered:**

### 4.6 Quad-Vector Floating-Point Compare Instructions

## Quad-Vector Floating-point TeST for NAN X-form

qvftstnan QRT,QRA,QRB

| 4 | QRT | QRA | QRB | 64 | /  |

|---|-----|-----|-----|----|----|

| 0 | 6   | 11  | 16  | 21 | 31 |