RZ 3387 (# 93433) 12/17/01 Electrical Engineering 200 pages

# **Research Report**

# **On Packet Switch Design**

Cyriel Minkenberg

IBM Research Zurich Research Laboratory 8803 Rüschlikon Switzerland

LIMITED DISTRIBUTION NOTICE

This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g., payment of royalties). Some reports are available at http://domino.watson.ibm.com/library/Cyberdig.nsf/home.

## **On Packet Switch Design**

Cyriel Minkenberg

IBM Research, Zurich Research Laboratory, 8803 Rüschlikon, Switzerland

## Abstract

Growth in communication network capacity has been fueled by rapid advances in fiber-optic transmission technologies. In contrast, growth in the capacity of switching and routing nodes has grown at a much slower pace, to the point where they are currently the bottlenecks that limit network capacity. The maximum capacity (throughput) a packet switch can achieve is largely determined by its architecture. It is widely recognized that conventional architectures cannot be scaled to implement the multi-terabit/s fabrics that will soon be required. Therefore, the problem this dissertation addresses is that of scalable high-capacity packet switches with a strong focus on performance.

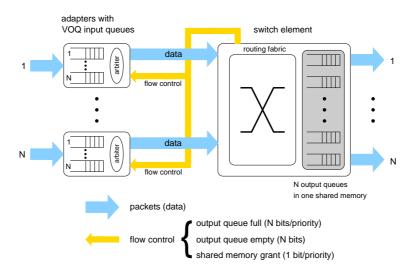

First, a comprehensive overview of current packet-switch architectures is given, in which the pros and cons of existing approaches are identified. The main contribution of this dissertation is the introduction and evaluation of a novel architecture that combines the strengths of input-queued switches using virtual output queuing (VOQ) and shared-memory output-queued switches. When compared to purely input-queued switches or combined switches with a limited speed-up, the need for centralized arbitration is removed, whereas when compared to traditional purely output-buffered switches the proposed architecture requires only a relatively small amount of costly output buffers. Performance of the proposed architecture is shown to be high and robust under a wide variety of traffic patterns, particularly when compared with existing architectures. A detailed study on the implementation aspects of the proposed architecture demonstrates its feasibility.

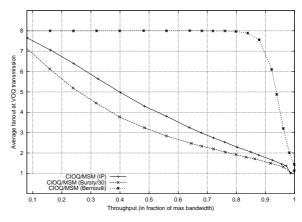

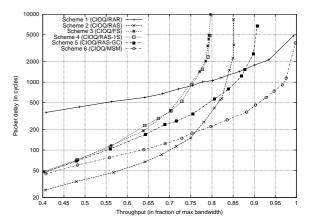

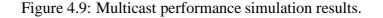

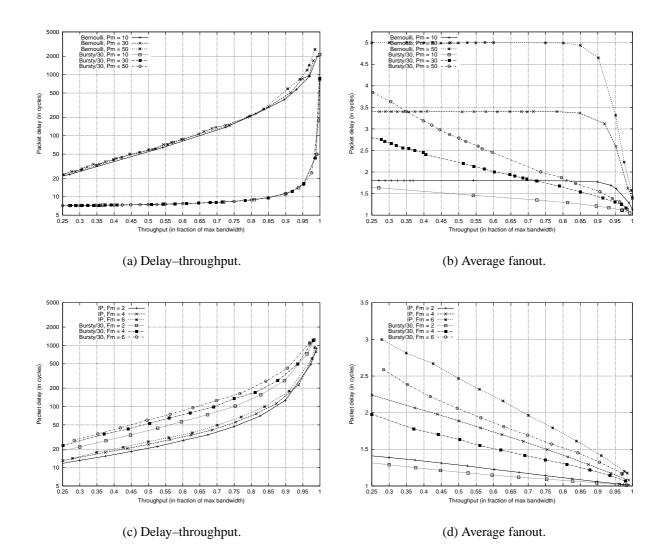

A VOQ-based multicast approach that integrates unicast and multicast queuing and scheduling disciplines is introduced, and is shown to outperforms the existing dedicated-multicast-queue approaches by far, and a straightforward, inexpensive implementation is described.

Finally, a method to support long packets is introduced. Because these long packets have to share resources in the switch (the output queues and the shared memory), deadlocks can occur if no precautions are taken. We demonstrate how a suitable modification of the flowcontrol mechanism can eliminate all possible deadlocks in the presence of both unicast and multicast traffic, as well as with multiple traffic priorities. To assess its complexity, a possible implementation is described in detail.

This dissertation<sup>\*</sup> has been performed in the context of the PRIZMA project (the IBM family of high-speed packet-switch chips). Its main role within this project has been system-level modeling and simulation. The main contributions in this context are that it has greatly increased understanding of the proposed system in terms of system-level architecture and performance, and, as a direct result of this increased insight, has paved the way for further architectural improvements.

\*PhD Thesis, Eindhoven University of Technology, The Netherlands, 2001.

# Contents

## Abbreviations

| 1 Introduction                               |     |         |                                                |    |

|----------------------------------------------|-----|---------|------------------------------------------------|----|

|                                              | 1.1 | Motiva  | ation                                          | 1  |

|                                              | 1.2 | The Pr  | oblem Domain                                   | 7  |

|                                              | 1.3 | Design  | 1 Task                                         | 9  |

|                                              | 1.4 | Disser  | tation Organization                            | 9  |

|                                              | 1.5 | Summ    | ary                                            | 9  |

| 2 An Overview of Packet-Switch Architectures |     |         |                                                |    |

|                                              | 2.1 | Classif | fication of Switch Architectures               | 11 |

|                                              |     | 2.1.1   | Blocking and non-blocking switch architectures | 12 |

|                                              |     | 2.1.2   | Sequence-preserving                            | 12 |

|                                              |     | 2.1.3   | Single-stage vs. multi-stage switches          | 12 |

|                                              |     | 2.1.4   | Buffer placement                               | 14 |

|                                              | 2.2 | No Qu   | euing                                          | 14 |

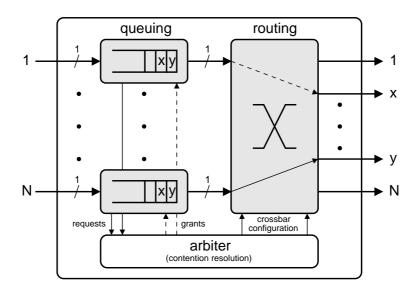

|                                              | 2.3 | Input ( | Queuing                                        | 15 |

|                                              |     | 2.3.1   | Implementations                                | 17 |

|                                              |     | 2.3.2   | Improvements                                   | 17 |

|                                              |     | 2.3.3   | Other variations                               | 19 |

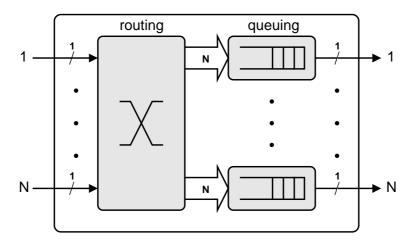

|                                              | 2.4 | Output  | t Queuing                                      | 20 |

|                                              |     | 2.4.1   | Examples                                       | 21 |

|                                              |     | 2.4.2   | Variations                                     | 24 |

|                                              | 2.5 | Shared  | l Queuing                                      | 24 |

|                                              |     | 2.5.1   | Shared input queuing                           | 25 |

|                                              |     | 2.5.2   | Shared output queuing                          | 26 |

|                                              | 2.6 | Virtual | Output Queuing                                 | 31 |

|                                              |     | 2.6.1   | Bipartite Graph Matchings                      | 33 |

|   |     | 2.6.2  | Maximum Size Matching                             | 34 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 2.6.3  | Maximum Weight Matching                           | 34 |

|   |     | 2.6.4  | Heuristic Matchings                               | 35 |

|   |     | 2.6.5  | An Implementation: Tiny Tera                      | 45 |

|   |     | 2.6.6  | Variations                                        | 46 |

|   | 2.7 | Combi  | ined Input and Output Queuing                     | 46 |

|   |     | 2.7.1  | Introduction                                      | 46 |

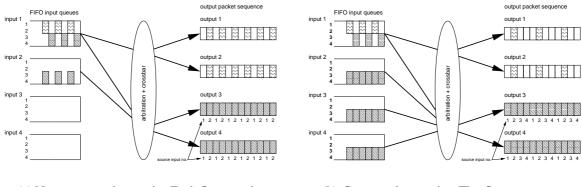

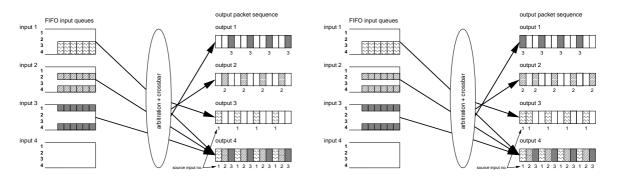

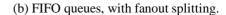

|   |     | 2.7.2  | CIOQ architectures with FIFO input queues         | 47 |

|   |     | 2.7.3  | CIOQ with finite output buffers and back-pressure | 49 |

|   |     | 2.7.4  | Emulation of ideal output queuing                 | 52 |

|   | 2.8 | Conclu | usions                                            | 53 |

|   |     | 2.8.1  | Input queuing                                     | 53 |

|   |     | 2.8.2  | Output queuing                                    | 55 |

|   |     | 2.8.3  | Combined input and output queuing                 | 56 |

| 2 |     | 1.     |                                                   |    |

| 3 |     |        | ed Input/Output-Queued Packet Switch Architecture | 57 |

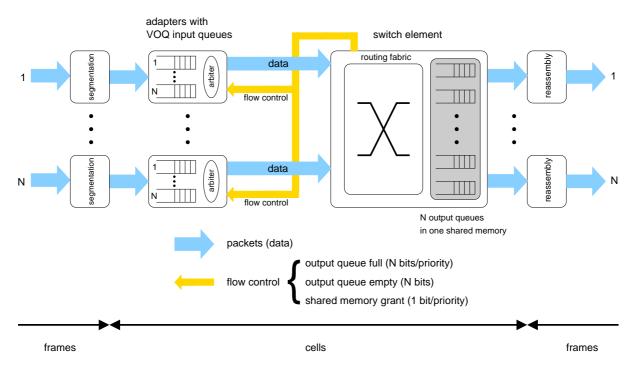

|   | 3.1 |        | iew                                               | 57 |

|   | 3.2 |        |                                                   | 57 |

|   |     | 3.2.1  | Design principles                                 | 57 |

|   |     | 3.2.2  | Grant-based flow control                          | 58 |

|   |     | 3.2.3  | VOQ selection algorithm                           | 59 |

|   |     | 3.2.4  | VOQ arbitration analysis                          | 61 |

|   |     | 3.2.5  | Memory sharing by means of OQ grant               | 64 |

|   | 3.3 | •      | ghput Analysis under Uniform Traffic              | 65 |

|   |     | 3.3.1  | Assumptions and definitions                       | 65 |

|   |     | 3.3.2  | Saturation under uniform traffic                  | 66 |

|   |     | 3.3.3  | Ideal OQ emulation                                | 67 |

|   |     | 3.3.4  | Buffer sizing                                     | 68 |

|   | 3.4 | Perfor | mance Simulation Results                          | 69 |

|   |     | 3.4.1  | Introduction                                      | 69 |

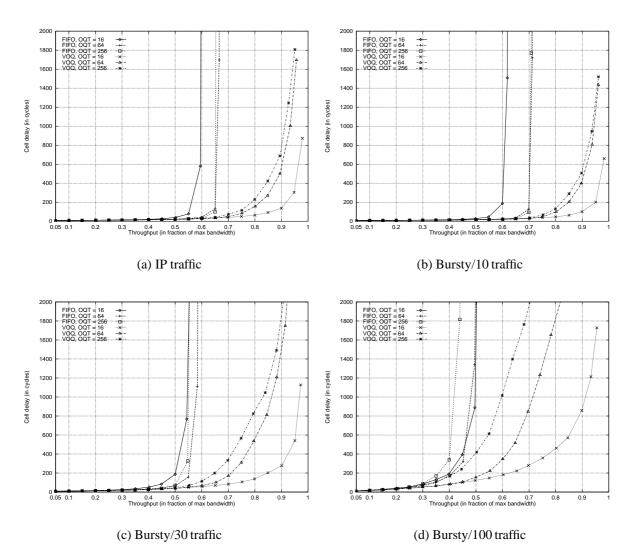

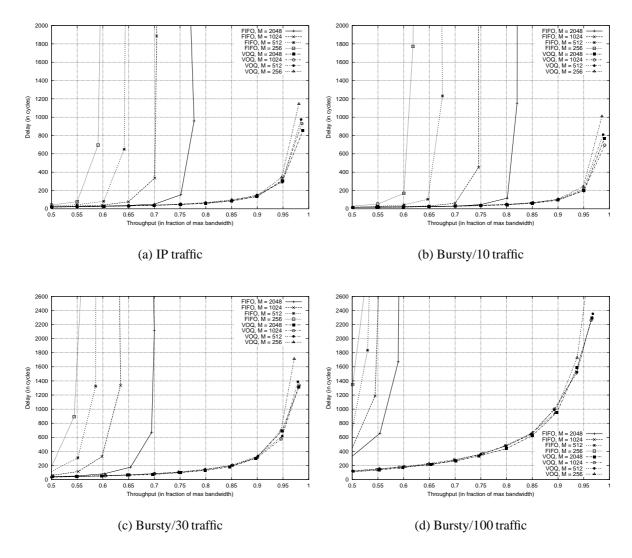

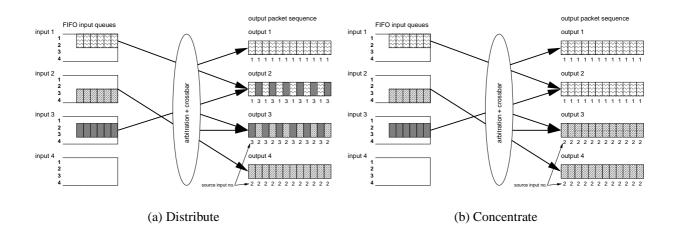

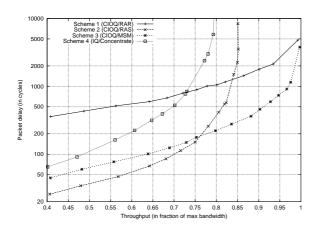

|   |     | 3.4.2  | FIFO vs. VOQ input queues and memory sharing      | 70 |

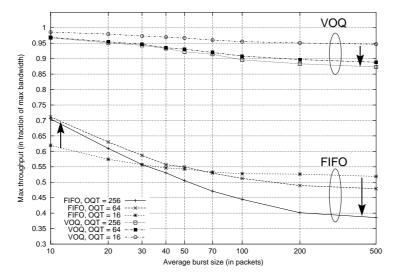

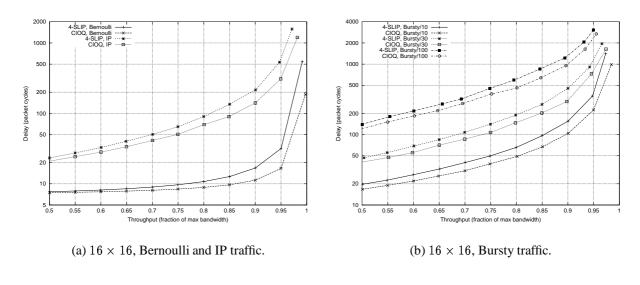

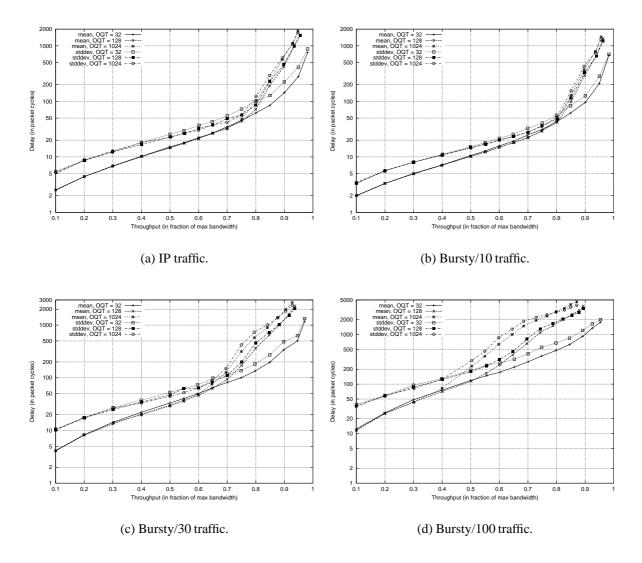

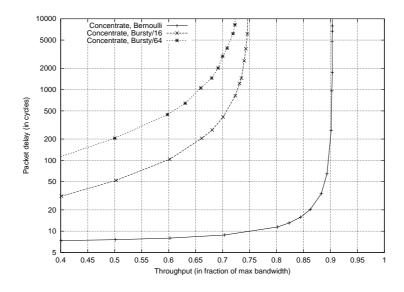

|   |     | 3.4.3  | Burst sensitivity                                 | 72 |

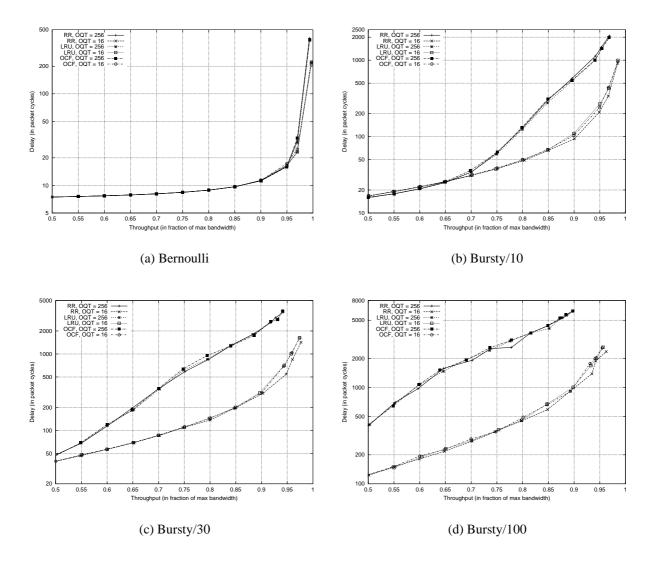

|   |     | 3.4.4  | VOQ selection policy                              | 73 |

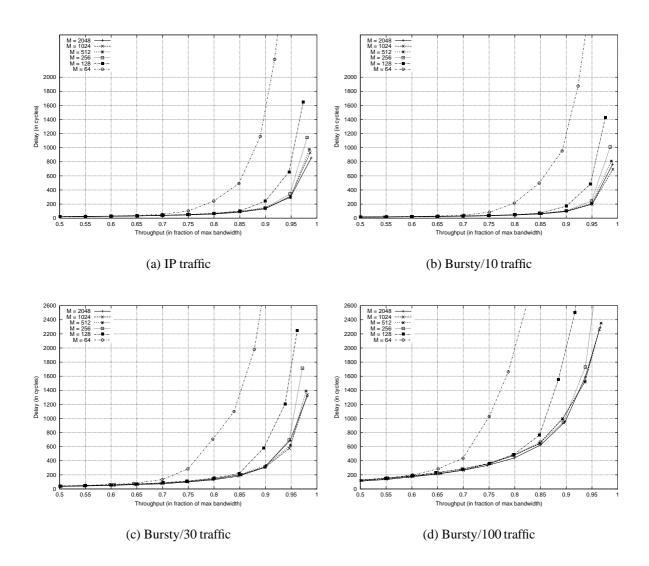

|   |     | 3.4.5  | Memory sizing                                     | 74 |

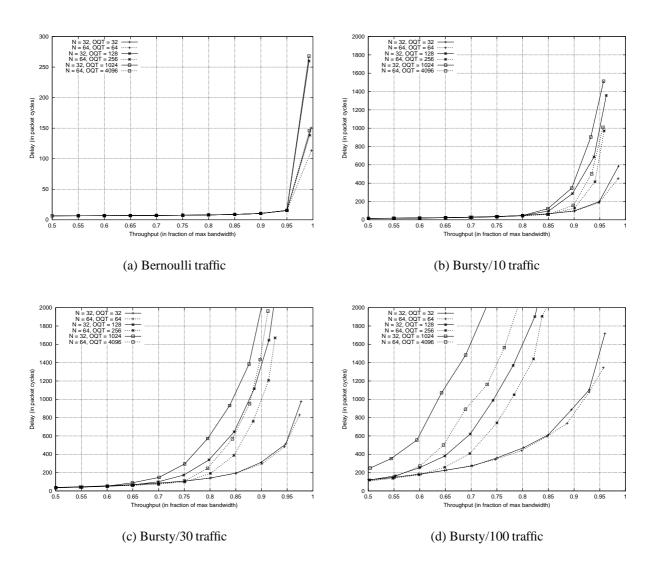

|   |     | 3.4.6  | Switch size                                       | 77 |

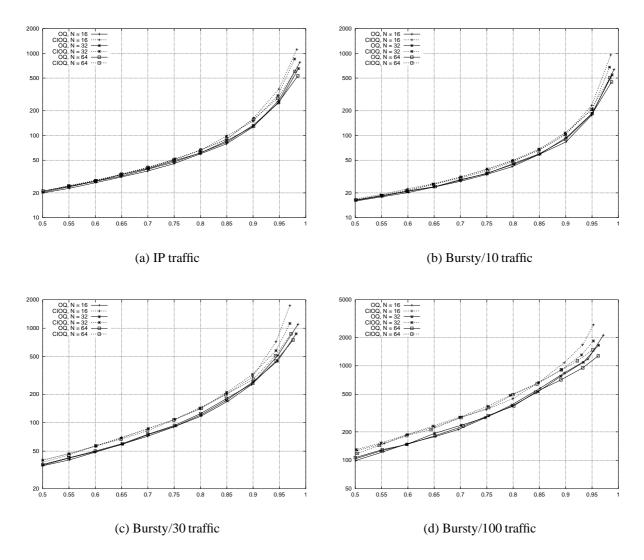

|   |     | 3.4.7  | Comparison with ideal OQ switch                   | 79 |

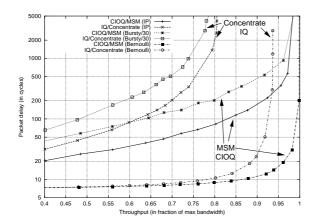

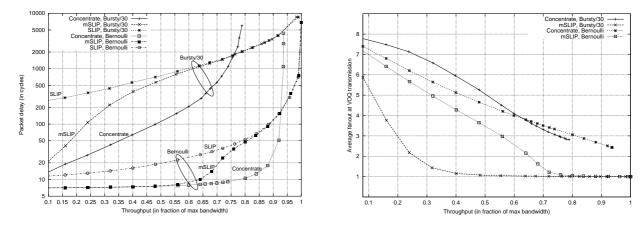

|   |                  | 3.4.8          | Comparison with input-queued architecture                                              |  |

|---|------------------|----------------|----------------------------------------------------------------------------------------|--|

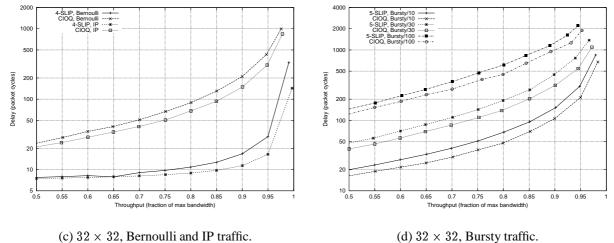

|   |                  | 3.4.9          | Low-degree traffic                                                                     |  |

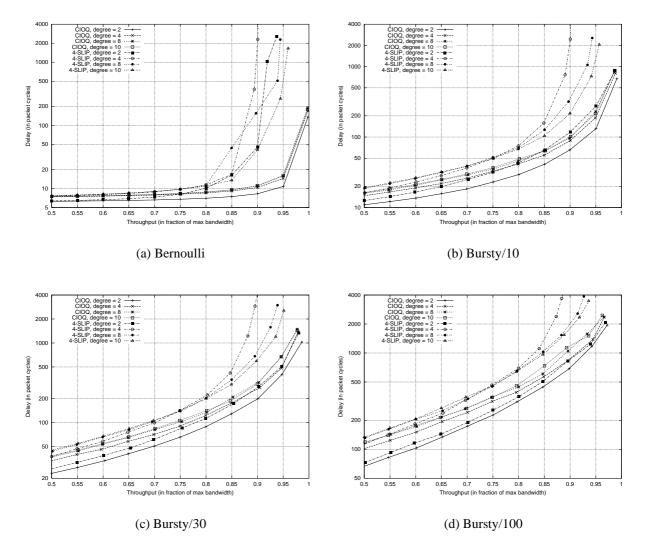

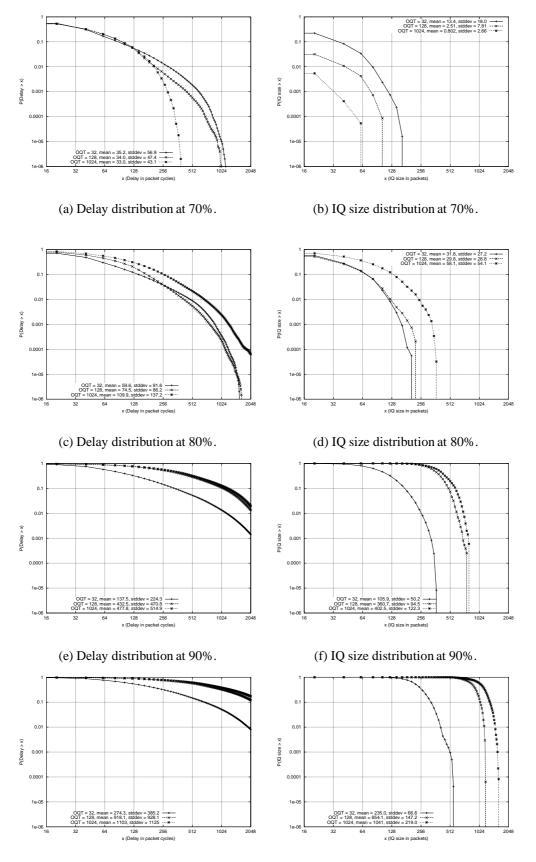

|   |                  | 3.4.10         | Input queue size distributions                                                         |  |

|   | 3.5              | Queue          | Empty Optimization                                                                     |  |

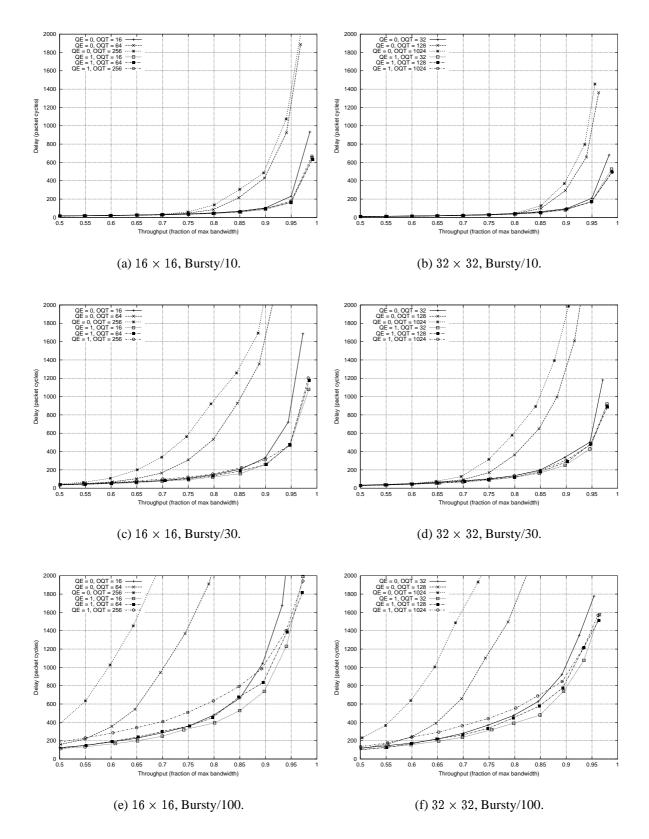

|   |                  | 3.5.1          | Performance simulation results                                                         |  |

|   |                  | 3.5.2          | Conclusion                                                                             |  |

|   | 3.6              | Implen         | nentation                                                                              |  |

|   |                  | 3.6.1          | Switch element                                                                         |  |

|   |                  | 3.6.2          | Flow control                                                                           |  |

|   |                  | 3.6.3          | Input queues                                                                           |  |

|   | 3.7              | Conclu         | sions                                                                                  |  |

| 4 | N/I14            | liaast         | 99                                                                                     |  |

| 4 |                  | ticast         |                                                                                        |  |

|   | 4.1<br>4.2       |                |                                                                                        |  |

|   | 4.2              |                |                                                                                        |  |

|   |                  | 4.2.1<br>4.2.2 |                                                                                        |  |

|   |                  | 4.2.2          | Input-Queued Switches                                                                  |  |

|   | 4.3              |                | Open Issues         102           ecture         104                                   |  |

|   | 4.5<br>4.4       |                | g Approaches                                                                           |  |

|   | 4.4              | 4.4.1          | $2^N$ Multicast Queues                                                                 |  |

|   |                  | 4.4.1          |                                                                                        |  |

|   |                  | 4.4.2          | Duplication at Input Buffer (RAR)    105      Single Dedicated Multicast Output    106 |  |

|   | 15               |                | Single Dedicated Multicast Queue                                                       |  |

|   | 4.5              |                | d and Algorithm108Design Principles108                                                 |  |

|   |                  | 4.5.1<br>4.5.2 |                                                                                        |  |

|   | 4.6              |                | Multicast Split/Merge (MSM) Algorithm       109         nentation       110            |  |

|   | 4.0<br>4.7       |                | nance                                                                                  |  |

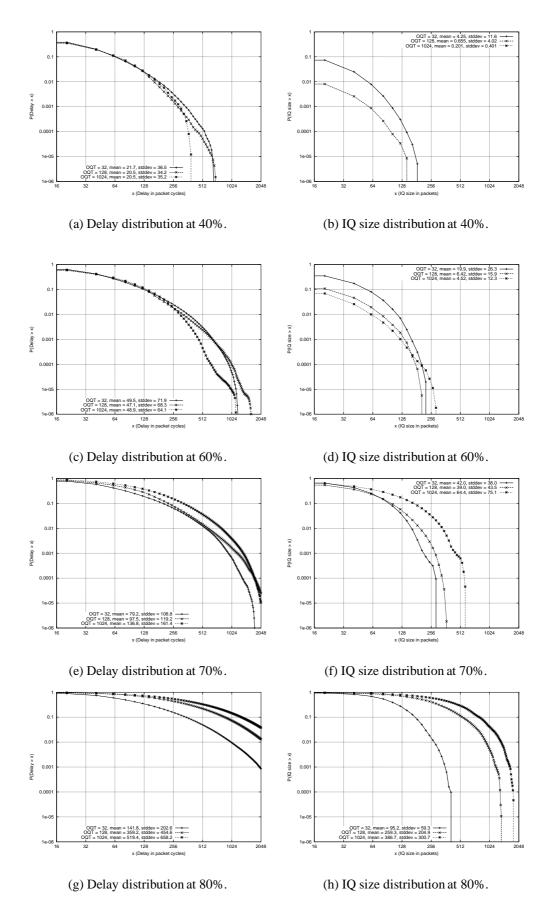

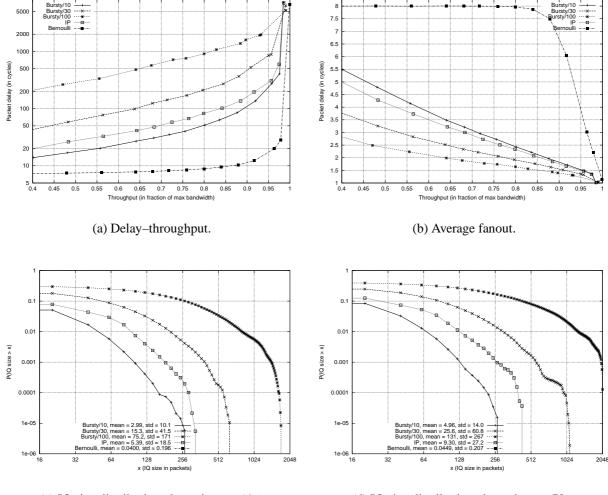

|   | 4./              | 4.7.1          | Delay–Throughput Characteristics                                                       |  |

|   |                  | 4.7.1          | Fanout at VOQ Transmission Point                                                       |  |

|   |                  | 4.7.2          | Mix of unicast and multicast traffic                                                   |  |

|   |                  | 4.7.3          |                                                                                        |  |

|   |                  | 4.7.4<br>4.7.5 | IQ size distribution                                                                   |  |

|   | 4.8              |                | n Input-Queued Switches                                                                |  |

|   | 4.9 Conclusions  |                |                                                                                        |  |

|   |                  |                |                                                                                        |  |

|   | <del>4</del> .10 | Discussion     |                                                                                        |  |

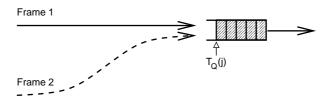

| 5                    | Frame Mode |                              |                                 |     |

|----------------------|------------|------------------------------|---------------------------------|-----|

|                      | 5.1        | Introdu                      | uction                          | 123 |

|                      | 5.2        | System                       | Description                     | 124 |

|                      | 5.3        | Frame                        | Mode                            | 126 |

|                      | 5.4        | Unicas                       | t Deadlock Prevention           | 126 |

|                      | 5.5        | Multica                      | ast Deadlock Prevention         | 128 |

|                      | 5.6        | Cyclic                       | Waiting Deadlock                | 129 |

|                      | 5.7        | Deadlo                       | ck-Free Scheduling Policy       | 133 |

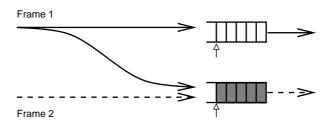

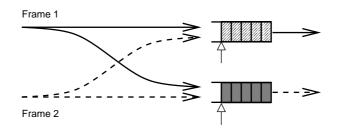

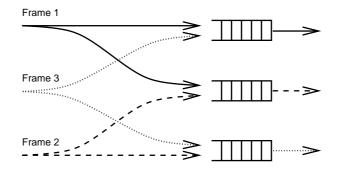

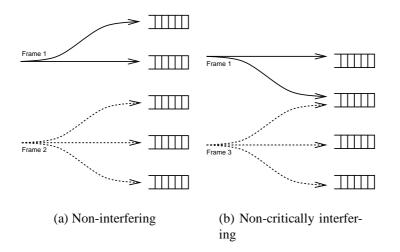

|                      |            | 5.7.1                        | Non-interfering sets            | 134 |

|                      |            | 5.7.2                        | Non-critically interfering sets | 134 |

|                      |            | 5.7.3                        | Critically interfering sets     | 134 |

|                      |            | 5.7.4                        | Examples                        | 134 |

|                      | 5.8        | Frame                        | Mode and Priorities             | 135 |

|                      | 5.9        | Practic                      | al Implementation               | 137 |

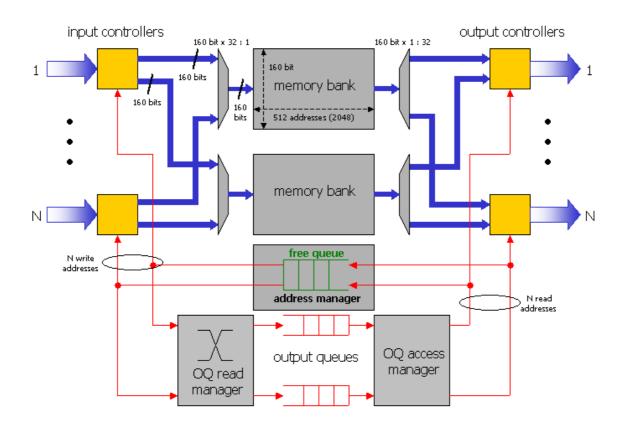

|                      |            | 5.9.1                        | Shared Memory                   | 137 |

|                      |            | 5.9.2                        | Frame Mode                      | 137 |

|                      |            | 5.9.3                        | Output Queues                   | 138 |

|                      | 5.10       | Conclu                       | sions                           | 143 |

| 6                    | A Pr       | actical                      | Application: The PRIZMA Switch  | 145 |

| U                    | 6.1        |                              | RIZMA Switch Family             |     |

| -                    |            |                              | 1A Features                     |     |

|                      |            | ility                        |                                 |     |

|                      | 0.5        |                              | Speed expansion                 |     |

|                      |            | 6.3.2                        | Single-stage port expansion     |     |

|                      |            |                              | /-of-Service Support            |     |

|                      | 0.1        | 6.4.1                        | Preemptive priorities           |     |

|                      |            | 6.4.2                        | Virtual lanes                   |     |

|                      |            | 6.4.3                        | Credit table                    |     |

|                      |            | 6.4.4                        | Best-effort traffic             |     |

|                      | 6.5        | - · ·                        | ast Support                     |     |

| 6.6 Link Paralleling |            |                              |                                 |     |

|                      |            | ontext of the PRIZMA Project |                                 |     |

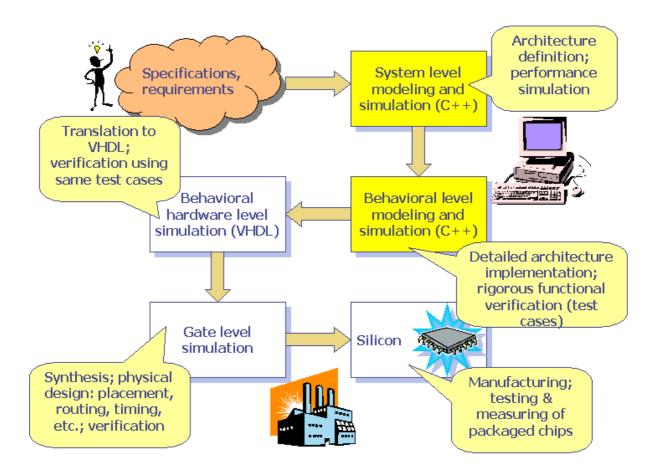

|                      | 0.7        | 6.7.1                        | Design methodology              |     |

|                      |            | 6.7.2                        | Impact of the work              |     |

|                      |            | 6.7.3                        | Shared-memory implementation    |     |

|                      |            | 0.7.5                        |                                 | 100 |

|    |                                            | 6.7.4    | Partitioning per output                     | 159 |  |

|----|--------------------------------------------|----------|---------------------------------------------|-----|--|

|    |                                            | 6.7.5    | Partitioning per input                      | 159 |  |

|    |                                            | 6.7.6    | Buffered crossbar                           | 160 |  |

|    |                                            | 6.7.7    | Conclusion                                  | 162 |  |

| 7  | Con                                        | clusions | s and Future Work                           | 163 |  |

|    | 7.1                                        | Contri   | butions                                     | 163 |  |

|    |                                            | 7.1.1    | Distributed Contention Resolution           | 164 |  |

|    |                                            | 7.1.2    | Output-Buffer-Sharing Strategies            | 164 |  |

|    |                                            | 7.1.3    | Distributed Fair Multicasting Scheme        | 165 |  |

|    |                                            | 7.1.4    | Deadlock-Free Frame Mode                    | 165 |  |

|    | 7.2                                        | Future   | Work                                        | 165 |  |

|    |                                            | 7.2.1    | Adaptive buffer sharing                     | 165 |  |

|    |                                            | 7.2.2    | Real-world traffic patterns                 | 166 |  |

|    |                                            | 7.2.3    | QoS mechanisms                              | 166 |  |

|    |                                            | 7.2.4    | Multi-stage fabrics                         | 166 |  |

|    |                                            | 7.2.5    | Parallel packet switches                    | 166 |  |

|    |                                            | 7.2.6    | Optical and hybrid electro-optical switches | 166 |  |

| Bi | bliogi                                     | raphy    |                                             | 166 |  |

|    | U                                          |          |                                             |     |  |

| A  | Buff                                       | erless S | Switch Throughput                           | 183 |  |

| B  | On Frame Interleaving vs. Non-Interleaving |          |                                             |     |  |

| С  | Perf                                       | ormanc   | ce Simulation Environment                   | 189 |  |

|    | C.1                                        | Introdu  | uction                                      | 189 |  |

|    | C.2                                        | Enviro   | onment                                      | 189 |  |

|    | C.3                                        | Simula   | ation Library                               | 190 |  |

|    |                                            | C.3.1    | Simulator concepts                          | 190 |  |

|    |                                            | C.3.2    | Communication concepts                      | 191 |  |

|    |                                            | C.3.3    | Statistics gathering                        | 192 |  |

|    |                                            | C.3.4    | Random numbers                              | 193 |  |

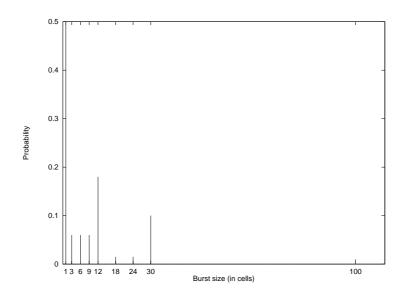

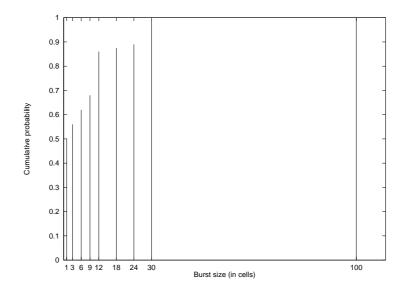

|    | C.4                                        | Traffic  | Models                                      | 193 |  |

|    |                                            | C.4.1    | Inter-arrival time distributions            | 193 |  |

|    |                                            | C.4.2    | Destination distributions                   | 195 |  |

|    | C.5                                        | Systen   | n Model                                     | 198 |  |

# Abbreviations

| CIOQCombined Input- and<br>Output-QueuedOQOutput Queue/Queued/Queuing<br>Output Queue ThresholdCMOSComplementary Metal-Oxide<br>SemiconductorPIMParallel Iterative Matching<br>Parallel Packet SwitchCNNCellular Neural NetworksSLIP(Not an abbreviation, "slip"<br>refers to the desynchronizationCPIClustered Processor Interconnect<br>DDrefers to the desynchronization<br>of grant arbiters that isDECDigital Equipment Corporation<br>MultiplexingQoSQuality of Service<br>VOQFARRFair Arbitrated Round RobinWBAWeight-Based Algorithm | ATM    | Asynchronous Transfer Mode       | OCF                 | Oldest Cell First                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------|---------------------|----------------------------------|

| Output-QueuedOQTOutput Queue ThresholdCMOSComplementary Metal-OxidePIMParallel Iterative MatchingSemiconductorPPSParallel Packet SwitchCNNCellular Neural NetworksSLIP(Not an abbreviation, "slip"CPIClustered Processor Interconnectrefers to the desynchronizationDDDelay Distributionof grant arbiters that isDECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm        | CIOQ   | -                                | 00                  | Output Queue/Queued/Queuing      |

| CMOSComplementary Metal-Oxide<br>SemiconductorPIM<br>PPSParallel Iterative Matching<br>Parallel Packet SwitchCNNCellular Neural NetworksSLIP(Not an abbreviation, "slip"CPIClustered Processor Interconnectrefers to the desynchronizationDDDelay Distributionof grant arbiters that isDECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                  |        | -                                | -                   | · · · ·                          |

| SemiconductorPPSParallel Packet SwitchCNNCellular Neural NetworksSLIP(Not an abbreviation, "slip"CPIClustered Processor Interconnectrefers to the desynchronizationDDDelay Distributionof grant arbiters that isDECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                         | CMOS   | · ·                              | PIM                 | · ·                              |

| CPIClustered Processor Interconnectrefers to the desynchronizationDDDelay Distributionof grant arbiters that isDECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                                                                                                                          |        | Semiconductor                    | PPS                 | Parallel Packet Switch           |

| DDDelay Distributionof grant arbiters that isDECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                                                                                                                                                                                            | CNN    | Cellular Neural Networks         | SLIP                | (Not an abbreviation, "slip"     |

| DECDigital Equipment Corporationcharacteristic of the algorithm)DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                                                                                                                                                                                                                                         | CPI    | Clustered Processor Interconnect |                     | refers to the desynchronization  |

| DWDMDense Wavelength-DivisionQoSQuality of ServiceMultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                                                                                                                                                                                                                                                                                                         | DD     | Delay Distribution               |                     | of grant arbiters that is        |

| MultiplexingVOQVirtual Output Queue(d/ing)FARRFair Arbitrated Round RobinWBAWeight-Based Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                           | DEC    | Digital Equipment Corporation    |                     | characteristic of the algorithm) |

| FARR Fair Arbitrated Round Robin WBA Weight-Based Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DWDM   | Dense Wavelength-Division        | QoS                 | Quality of Service               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | Multiplexing                     | VOQ                 | Virtual Output Queue(d/ing)      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FARR   | Fair Arbitrated Round Robin      | WBA                 | Weight-Based Algorithm           |

| FCFS First-Come First-Served WDM Wavelength-Division Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FCFS   | First-Come First-Served          | WDM                 | Wavelength-Division Multiplexing |

| FIFO First-In First-Out WFQ Weighted Fair Queuing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FIFO   | First-In First-Out               | WFQ                 | Weighted Fair Queuing            |

| FIRM FCFS In Round-robin RAR Replication At Receiving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIRM   | FCFS In Round-robin              | RAR                 | 1 0                              |

| Matching RAS Replication At Sending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 0                                |                     |                                  |

| GbpsGigabits per secondRRRound Robin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -      | 0 1                              |                     |                                  |

| GBpsGigabytes per secondRRMRound-Robin Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | • • •                            |                     |                                  |

| GTI Gran Turismo Injection RPA Reservation with Preemption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | e e                              | RPA                 | -                                |

| HoL Head-of-Line and Acknowledgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                  |                     | 6                                |

| IBM International Business Machines PRIZMA <sup>1</sup> Parallel Routing In                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                  | PRIZMA <sup>1</sup> |                                  |

| i.i.d. independently and identically Zurich's Modular Architecture;                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | i.i.d. |                                  |                     |                                  |

| distributed Packetized Routing Integrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                  |                     | • •                              |

| IPInternet ProtocolZurich Modular Architecture;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                  |                     |                                  |

| IQ Input Queue/Queued/Queuing Packetized Routing In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -      | · · · ·                          |                     | e                                |

| IQDInput Queue size DistributionZurich's Modular Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -      | 1 -                              |                     | Zurich's Modular Approach        |

| iSLIP Iterative SLIP (see also SLIP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                  |                     |                                  |

| LCFS Last-Come-First-Served                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                  |                     |                                  |

| LOOFA Lowest Output queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LOOFA  |                                  |                     |                                  |

| Occupancy First Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                  |                     |                                  |

| LRU Least Recently Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | •                                |                     |                                  |

| MEMS Micro-Electro-Mechanical System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | •                                |                     |                                  |

| MFT Memory Full Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                  |                     |                                  |

| NHD         Networking Hardware Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NHD    | Networking Hardware Division     |                     |                                  |

<sup>1</sup>A concensus on the precise meaning of this acronym has not yet been reached.

# **Chapter 1**

# Introduction

This chapter starts with the motivation of the work presented in this dissertation, and proceeds to introduce the main topic and detail the design task. Finally, the organization of the dissertation is explained.

# 1.1 Motivation

### The need to communicate

Throughout history, humans have always had a need to communicate. Because of the central role communication plays in human society, inventions that impact communications also tend to have a drastic impact on society as a whole. Next to the invention of the printed word (Johannes Gutenberg, 1446), the telegraph (Samuel Morse, 1835) and the telephone (Alexander Bell, 1876) represent the greatest revolutions in communications. The next revolution, brought about by the merging of digital computer and communications technologies, has opened up an entire new dimension of communication, with the Internet, and in particular the bandwidthhogging World Wide Web, as one of its most prominent exponents. With the arrival of the Information Age as successor to the Industrial Age, demand for communication bandwidth has been growing explosively, best exemplified by the exponential growth curves of the Internet. More importantly, this trend shows no sign whatsoever of slowing down. On the contrary, numerous new applications are being proposed that will drive demand for communication bandwidth at an even faster pace. The widespread deployment of applications such as audio- and videostreaming, the conduction of business-to-consumer and business-to-business transactions, and the integration of wireless communications with the Internet are expected to be a driving force behind this trend.

#### Structure of communication networks

The infrastructure that has to support this communication is faced with rapidly increasing demand, which is the main motivation behind this work. Before going deeper into details, let us have a closer look at the general structure of communication networks. From the end-user's viewpoint, it would be ideal to have a dedicated connection between any pair of end-users in a network, because this offers known, deterministic latency, throughput and availability characteristics. A pair of communicating users can never interfere with communication between any other pair. While these are certainly highly desirable features, the price to be paid is also very high: the complexity in terms interconnection links in such network with N users is on the order of  $N^2$ , which may be feasible for a network having just a few users, but for networks such as the public telephone system or the Internet with tens of millions or even hundreds of millions of users, such a solution is clearly both impractical and prohibitively expensive.

To overcome this interconnection complexity hurdle, we make the following assumptions:

- End-user bandwidth demand varies strongly over time.

- Given a sufficiently large group of *M* end users, the probability that the aggregated bandwidth demand from this group exceeds a certain threshold *T* can be made "acceptably" small (in circuit-switching this is called the *blocking* probability).

Now, in general the sum of the requested user bandwidth is much smaller than the total bandwidth available to the group, which offers the potential for substantial cost savings. To take advantage of this, traffic from this group of end users is aggregated (*multiplexed*) onto a single link of bandwidth T that will be shared by all of the users in the group.

#### **Statistical multiplexing**

This principle is called *statistical multiplexing* and is one of the most important design principles of any communication network, because it constitutes the key enabling factor for cost-effective deployment of ubiquitous high-speed communication networks.

Users with bandwidth demands that do not satisfy the above assumptions may be better off not sharing their bandwidth, which is why telecommunication operators also offer leased lines.

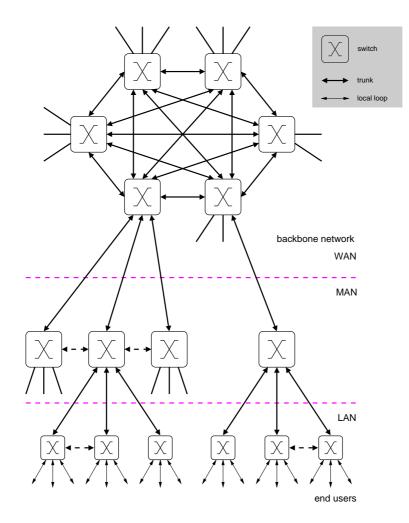

Applying the principle of statistical multiplexing boils down to segmenting the network. This is done by first assigning groups of users that will share a link, and then interconnecting the groups by means of *switching nodes* or *switches* for short. The main task of these nodes is to forward information arriving on their input links to the correct output links. In early telephony exchanges this was accomplished by means of electro-mechanical relay switches, hence the term "switching", which is still in use today. In the context of packet-switched networks, the nodes are typically called *routers*. The interconnecting transmission links are often called *trunks*. In large networks, there may be multiple hierarchical stages of segmentation, so that switches in a lower stage share links through the higher stages to achieve additional efficiency benefits from statistical multiplexing, see Fig. 1.1.

#### The great bandwidth gap: Optics vs. electronics

As described above, the main two components of a communication network are the transmission links ("transport") and the switching nodes. The transmission part of current highbandwidth networks is largely fiber-optic. Advances in fiber-optic transmission technologies such as wavelength-division multiplexing (WDM) and dense WDM (DWDM) have greatly pushed the envelope of bandwidth available in fibers by multiplexing large numbers of separate channels onto a single fiber. Each individual channel typically operates at the Optical

Figure 1.1: Hierarchical network structure. The switches act as statistical multiplexers in and between stages.

Carrier (OC-x) rates OC-48 (2.5 Gb/s), OC-192 (10 Gb/s), or even OC-768 (40 Gb/s). Using state-of-the-art DWDM techniques, a single fiber can carry over 5 terabit of data per second.<sup>1</sup>

Although silicon technologies have also advanced rapidly, the gap between the data rates that optical transmission technology can deliver and those that electronic switches can process is widening at an alarming rate. Worse still, in the foreseeable future certain fundamental physical limits of traditional CMOS silicon technology are expected to be reached. Unlike when bipolar silicon technology ran out of steam and CMOS was already around and mature enough to take over, there is no such emerging technology in sight yet that can replace CMOS within, say, the next five to ten years.<sup>2</sup> This means that the switching and routing nodes of the network are the bottleneck of the network, and will remain so for some time to come. Thus, it is of utmost importance that the switch be as efficient as possible in transferring packets from in- to outputs, to avoid further reduction in the usable link rate, i.e. as little bandwidth as possible should go unused and its throughput must be close to 100%.

3

<sup>&</sup>lt;sup>1</sup>Current laboratory DWDM setups [Bigo00] can multiplex as many as 128 colors, each color carrying an OC-768 channel, on one fiber, which adds up to 5.12 Tb/s.

<sup>&</sup>lt;sup>2</sup>The so-called double-gate transistor technology may provide further leeway.

As an alternative to electronic switches, all-optical switches have the advantages that light can be routed through free space, and that light can be carried over long distances with very little loss in signal power. With transport being almost entirely in the optical domain, such all-optical switches have the additional advantage of eliminating the expensive conversion from the optical to the electrical domain and back. However, they have two distinct disadvantages. First, most current optical switches can only switch fairly slowly (in the 1 to 10 ms range; faster optical switches do exist, but are prohibitively expensive), which prevents per-packet processing. Turner's "burst switching" scheme [Turner98, Turner99, Chen00b] aims at circumventing this problem by switching at the granularity of bursts, i.e., large, aggregated chunks of data that can be routed as a whole. Second, compared to its electronic equivalent, optical storage of information is very cumbersome and impractical.

Still, a number of all-optical switches are being developed, such as micro-electro-mechanicalsystem (MEMS) switches, thermo-optic switches, "bubble" (waveguide) switches, and liquidcrystal switches [Yao00, Bishop01].

Until optical buffering becomes feasible, optical switching granularity is improved, and optical switch technology becomes cost-competitive with its electronic counterpart, electronic switches will continue to play an important role. Hybrid solutions combining the strengths of the two technologies will certainly also be proposed in the meanwhile. By their respective natures, all-optical switches are better suited to circuit switching and electronic switches to packet switching.

#### Circuit and packet switching

Conventional circuit-switched networks such as the telephone system are unsuitable for data and computer communication because of the fundamentally different characteristics of the types of traffic. In contrast to the constant rate of voice traffic, data and computer communication traffic is typically very bursty. This makes it inherently unsuitable to be switched by a circuit-switched network, because such a network (a) employs dedicated communication paths, leading to poor utilization, (b) is based on fixed-rate bandwidth allocation, implying inflexibility of coping with widely varying bandwidth demands, and (c) incurs high call setup and teardown overheads, making it unsuitable for short-duration calls (cell-based networks using virtual circuit switching also suffer from this last disadvantage). These realizations led to the development of packetswitched techniques and networks, which overcome the afore-mentioned shortcomings, at the price of (a) complex routing and control, and (b) variable, unpredictable network performance in terms of loss rates, latency, jitter, and throughput. The key difference between switching nodes in a circuit- and a packet-switched network is that in the former, no queuing is required in the node because a dedicated path exists and arriving data is guaranteed to be able to leave (almost) immediately.<sup>3</sup> In the latter, however, packets from different sources can simultaneously contend for the same outgoing bandwidth, so that buffering is required to store packets that cannot be transmitted immediately. As we shall see later, the queuing discipline employed in a packet switch is paramount to its performance.

A strong argument for circuit switching is that moving from a packet-switched network to a circuit-switched network obviates the need for buffering, thus, perhaps, enabling fully optical

<sup>&</sup>lt;sup>3</sup>Some buffering may be required, such as in a time slot interchanger (TSI), but this buffering is strictly limited and deterministic.

switching.

For the finer details of both circuit- and packet-switched networks, the reader is referred to [Stallings92] for example. A useful book on computer networks in general is [Tanenbaum96].

#### On packets, cells, and frames

Current state-of-the-art semiconductor technologies allow the implementation of packet switching at transmission rates up to several Gb/s per link in VLSI hardware. For implementational complexity reasons, packet switching at the hardware level is usually tailored towards fixedlength packets. Therefore, in this dissertation, the term *packet* will be used for fixed-size data units, analogous to the term *cell*, which originates in the 53-byte data unit employed in Asynchronous Transfer Mode (ATM) networks. Typical packet sizes are in the range of 32 to 256 bytes. One *packet cycle* equals the duration of a single packet T = L/B, where L is the length of a packet in bits, and B the link rate in bits per second. When referring to data units of variable size, in the range of, say, 64 to 2,048 bytes, we will employ the term *frame*.

Note that these definitions may differ from those employed elsewhere in the literature.

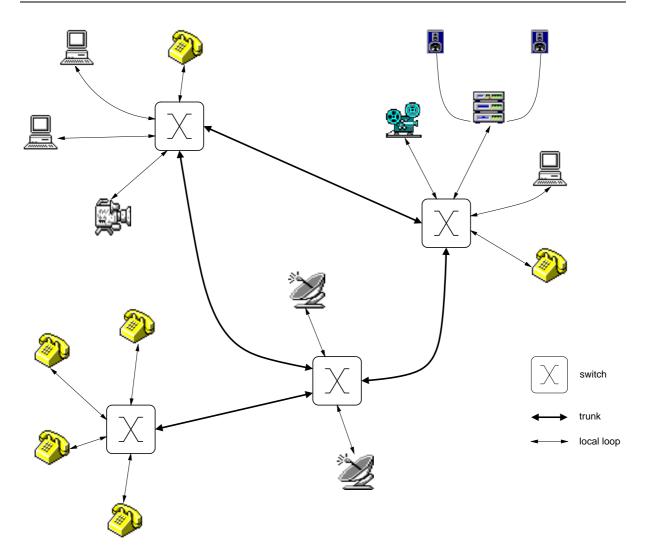

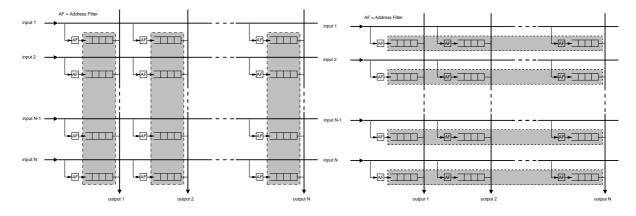

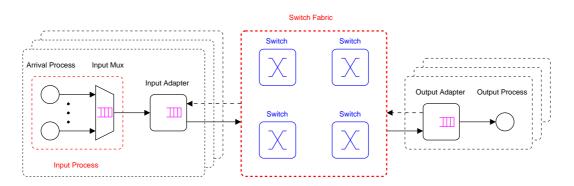

#### Switch and adapter functionality

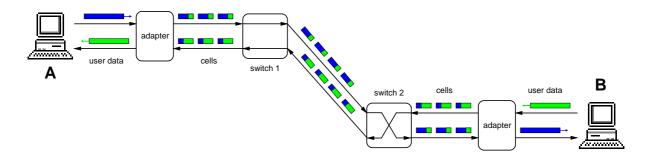

Fig. 1.2 depicts a fictitious network, consisting of four switches (represented by the rounded boxes), a number of trunks interconnecting the switches (represented by the thick two-headed arrows, indicating bi-directional communication), and a collection of various data sources and sinks, including speech-, audio-, video- and data-communication, which are all being transported simultaneously across the same network. Typically, each data source/sink connects to the network through an *adapter*, whose job it is to translate the incoming and outgoing data streams at both the logical and physical levels. This often entails segmenting the incoming data stream, which can take virtually any shape, into (fixed-length) data units (packets) that the network can transport, and then transmitting these packets using the protocols and the physical layer technology that the network the adapter is connected to understands. An adapter at the receiving end will have to reassemble the segments into the original data stream to reconstruct the signal. The job of the switches it is then to route the incoming packets to their proper destination. Both the adapter function and the routing function of the switch are illustrated in Fig. 1.3.

For the time being, we will not concern ourselves with how the entire route through the network is determined and established; this is a science in its own right. One way is to perform source routing, where the route is determined in advance, and store the local routing tags for each switch in the packet itself so that the packet is self-routing throughout the network. An alternative is to compute the route in advance (static routing), but have the local routing tags inserted before each switch, which requires that either switch or inter-switch adapters perform header translations. A third possibility is to do fully dynamic routing. In an environment where packet order must be maintained, this incurs additional complications. These issues are beyond the scope of this work.

Thus, packet-based switches are required to perform two basic functions:

5

Figure 1.2: A typical communication network consisting of data sources, sinks, trunks and switches.

- 1. **Routing**: Packets must be forwarded from their arriving input to one or more destination outputs, as indicated by their routing tags.

- 2. **Queuing**: Owing to the statistical nature of packet traffic, it may happen that packets arriving simultaneously at different inputs want to go to the same output. Only one packet can be routed directly, while the others have to wait. This state of (temporary) output overload is called *output contention*. To resolve the output contention without dropping all those packets that lose the contention, *buffers* are necessary that must be organized such that packet sequence is maintained<sup>4</sup> on a per virtual connection basis, i.e. *sequence integrity* must be maintained.

The way in which the queuing function is implemented is one of the distinguishing characteristics of a packet switch and, as will be seen, the determining factor in a packet switch's efficiency. Therefore, the topic of this dissertation is the design of fixed-length-packet switch

<sup>&</sup>lt;sup>4</sup>This requirement mainly stems from ATM, but is desirable also in other environments such as IP, where it is not strictly required.

7

Figure 1.3: Adapter function: Computer A generates data it wants to send to Computer B. The adapter segments the data into smaller, fixed-length units, prefixes these with the address of computer B, and forwards them to the network. The packets reach their destination through switches 1 and 2, and are reassembled into the original stream by the receiving adapter, which hands the data over to the final recipient.

architectures to achieve optimal link utilization (throughput), which, as argued before, is an essential characteristic given current trends, while maintaining fairness among all its inputs and outputs. Furthermore, the architecture must be amenable to implementation at aggregate throughput rates in the range of hundreds of Gb/s to 1 Tb/s range, and allow scaling to even larger systems.

The next section gives a short overview of the problem domain, existing solutions and their drawbacks, and outlines the direction in which this dissertation will proceed.

# **1.2 The Problem Domain**

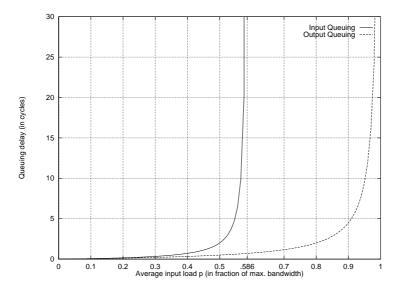

The two traditional approaches to solving contention in packet switches are input queuing and output queuing. Both methods have been the topic of many research efforts in the past and are therefore well understood. Output queuing has usually been favored, because of its inherent performance advantages over input queuing: theoretically, output queuing offers ideal performance. A packet switch is considered to be ideal if it is *work-conserving*, i.e., no output line should ever be idle as long as at least one packet destined to it is in the switch. Thus, it can easily be verified that an output-queued switch is indeed work-conserving given any traffic pattern. Additionally, as packets are immediately placed in a buffer on the port they are destined to, it is easy to control packet delay and delay variation in an output-queued switch and thus provide QoS guarantees to individual flows.

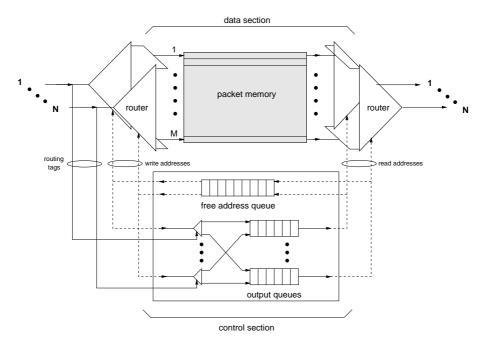

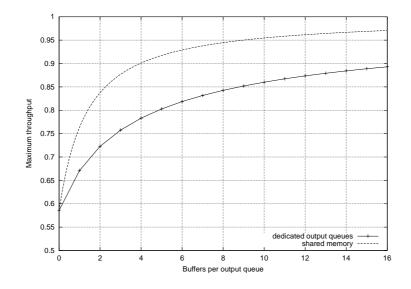

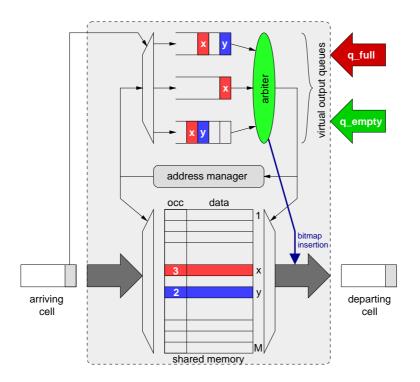

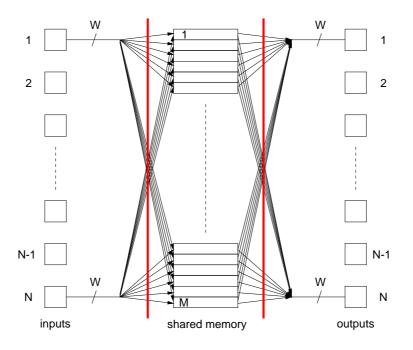

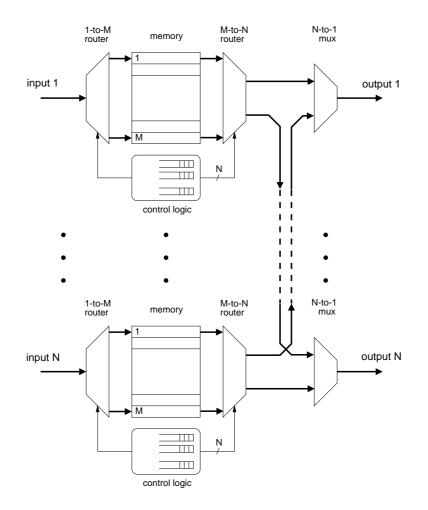

Output-queued switches are often implemented in a shared-memory architecture rather than with dedicated output queues mainly because of a performance advantage due to increased buffer efficiency: to achieve the same performance fewer buffers per output are needed. However, with ever-increasing bandwidth demands, it is becoming increasingly difficult to realize switches that purely rely on the shared-memory approach because the aggregate shared-memory bandwidth is proportional to both the line rate and the number of ports. This internal *speed-up factor*, inherent to output queuing, is the main implementational challenge for a shared-memory switch. Shared-memory implementations based on SRAMs are limited by the memory access time, which for current state-of-the-art SRAMs is around 5 ns. Assuming a 64-byte wide data path, this limits the achievable aggregate switch throughput to about 51.2 Gb/s. Higher rates can be achieved by more exotic memory implementations, which typically are very costly in terms of silicon (gates and wiring) area, thus strictly limiting the amount of memory that can be implemented on a single chip.

The inherent limitations encountered in implementing shared-memory switches have been the main motivation behind intense research efforts in input-queued architectures over the past several years.

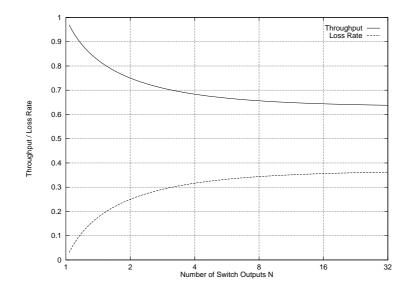

Contrary to its output-buffered counterpart, an input-buffered switch requires only buffers with a bandwidth proportional to the line rate, but *not* to the number of switch ports, seemingly making them inherently more scalable to higher line rates. However, classic input-queued architectures suffer from *head-of-line* blocking, owing to the use of FIFO queues. This means that a blocked packet at the head of the input queue can prevent packets behind it from reaching idle outputs, leading to severe throughput degradation. Recent research has been aimed at eliminating head-of-line blocking in input-queued switches, and raising their level of performance closer to that of output-queued switches.

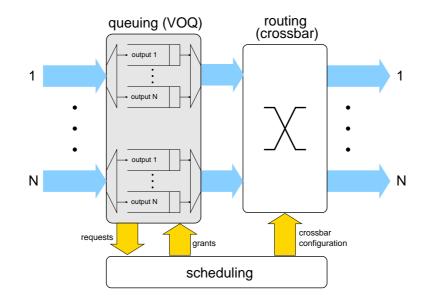

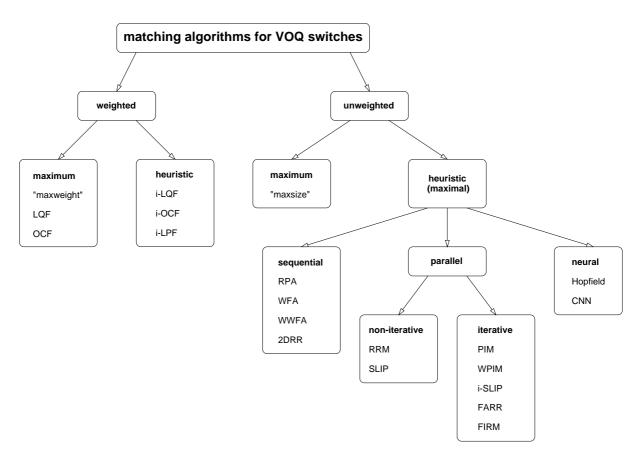

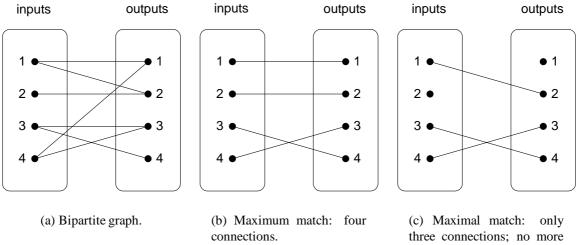

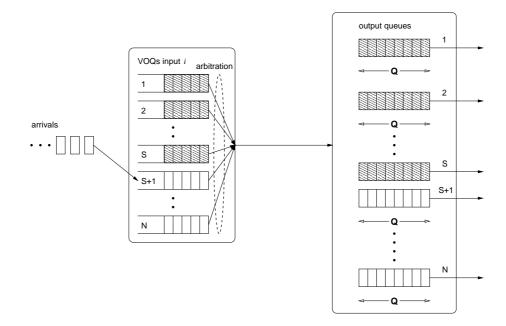

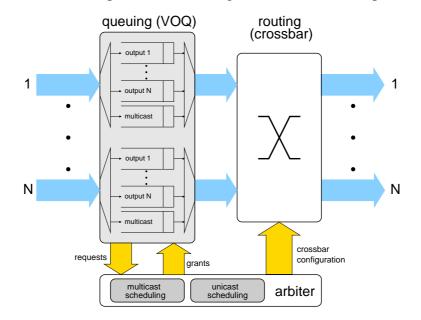

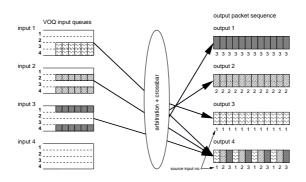

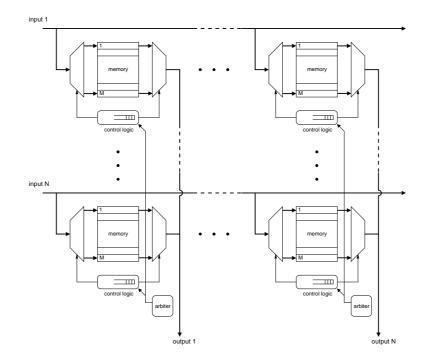

The solution most commonly adopted employs input queues that are sorted by destination, which gives rise to an architecture with  $N^2$  queues and a centralized scheduler that arbitrates among these queues. This arrangement, often referred to as *virtual output queuing* (VOQ) eliminates head-of-line blocking, but a suitable scheduling algorithm is required to obtain good performance. Unfortunately, the known optimal algorithms are too complex to implement at very high data rates, so sub-optimal, heuristic algorithms of lesser complexity, but also lesser performance, have to be used. The centralized scheduler is the bottleneck in this architecture in terms of implementational complexity. Furthermore, support for multicast and provisioning of QoS classes is substantially more difficult than in an output-queued architecture.

To summarize, we can say that switch architectures relying purely on output queuing cannot scale to high throughput because of memory bandwidth limitations, whereas purely inputqueued architectures are faced with a poorly scalable centralized scheduler. With the sharedmemory architecture the tradeoff is between memory bandwidth and memory size (which translates into switch performance), while with the input-queued architecture it is between scheduler complexity and switch performance.

These considerations have given rise to a third class of packet-switch architectures: the *combined input- and output-queued* (CIOQ) class. It is within this class of architectures that we expect to be able to find the key to improving on the existing, non-combined architectures.

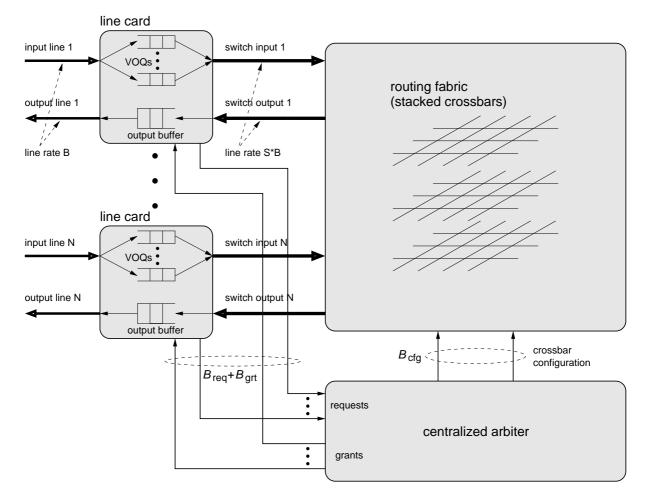

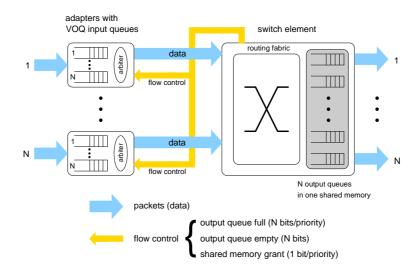

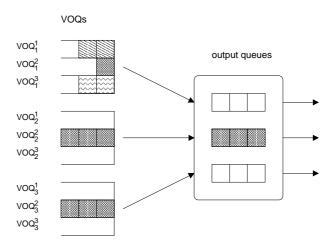

We conjecture that combining the core concepts of shared-memory output queuing and VOQ input queuing into one switch architecture using a simplified VOQ scheduling algorithm can lead to unique results.

Note that this Section has only provided a brief glimpse at the problem domain. Chapter 2 gives an extensive overview of existing packet-switch architectures and surveys the state-of-the-art within each of the classes of architectures.

# 1.3 Design Task

The goal is to derive a packet-switch architecture that offers close to ideal performance, guarantees fairness among all its inputs and outputs, behaves robustly under unfavorable traffic patterns, supports multicast traffic and QoS provisioning, can be implemented in VLSI at throughputs up to the Tb/s range at a reasonable cost, and is inherently scalable to more and/or faster ports. As indicated above, we will look at the class of CIOQ architectures to find a candidate architecture that fulfills these requirements.

# **1.4 Dissertation Organization**

This dissertation is structured as follows: Chapter 1 (this one) is a general introduction, containing a brief historical perspective, some background information on communication networks and the role of switching therein, and introduces the problem domain and the mission statement. Chapter 2 gives an overview of existing packet-switch architectures, categorized into three main classes of architectures based on queuing discipline. The state-of-the-art architectures in each class are reviewed and their merits and drawbacks assessed. Chapter 3 presents our novel CIOQ architecture. Its design principles are explained and its operation is detailed. We evaluate its performance under a range of traffic characteristics by means of both analysis and performance simulations, and compare it with existing approaches. Finally, we discuss implementational aspects and consider scalability issues. Chapter 4 proposes a novel method and algorithm for efficient and fair multicast support that can be integrated seamlessly into the switch architecture introduced in Chapter 3. We assess its performance characteristics by means of simulations and propose a straightforward hardware implementation. Chapter 5 describes the details of deadlock-free frame mode operation in the proposed architecture. Chapter 6 presents a practical application of the architecture and methods introduced in the previous two chapters, in the form of the PRIZMA family of packet switches. Finally, Chapter 7 summarizes the conclusions we arrived at in the course of the work presented in this dissertation, and indicates directions for future research.

# 1.5 Summary

Global bandwidth demand is growing at an exponential rate, fueled mainly by the proliferation of the Internet and its establishment as a worldwide communication medium encompassing a wide spectrum of applications. Optical transmission technologies such as wavelength-division multiplexing have allowed these growth rates to be sustained by offering a way to multiply the available transmission bandwidth in optical fibers by large factors. So far, the mainly electronic routing and switching network nodes have (in a way) been able to keep up by exploiting the advances in silicon technology, but already the available transmission bandwidth is starting to outstrip the available routing and switching capacity many times, a situation that is not likely to improve any time soon. All-optical switches are very promising to achieve very high throughput, but have two distinct disadvantages: first, their switching granularity is very coarse, which prevents per-packet switching, and second, optical buffering is cumbersome and impractical. Therefore, electronic packet switches are expected to continue to play a large role for a long time to come, provided that architectures that can scale to the desired throughput in the multi-terabit range are being developed. Thus, the aim of this dissertation is to develop a high-capacity, scalable, and practically realizable (using current technologies) packet-switch architecture.

# **Chapter 2**

# An Overview of Packet-Switch Architectures

We categorize packet-switch architectures based on queuing discipline, and provide an overview of existing packet-switch architectures, with the main focus on providing insight into the most recent developments in each class. The chapter concludes with a discussion on the merits and drawbacks of the most relevant architectures, based upon which the requirements for a new switch architecture, to be further developed in subsequent chapters, are established.

# 2.1 Classification of Switch Architectures

The purpose of this chapter is *not* to provide a comprehensive overview of all packet-switch architectures proposed over the past 10 to 15 years. This has been done quite adequately by a number of switch architecture overview papers, such as [Hluchyj88b], [Rathgeb88], [Ahmadi89b], [Tobagi90], and [Pattavina93]. A more recent overview focusing especially on space-division architectures is presented in [Awdeh95].

These papers use many different ways to classify switch architectures into categories. Some of these criteria are blocking vs. non-blocking, buffering strategy (input-buffered, output-buffered or combined), lossy vs. lossless, single-stage vs. multi-stage, buffer implementation (partitioned, grouped, shared), time- or space-divided (or combined TST/STS).

For the purpose of this dissertation many of these categorizations focus too strongly on implementation details. For instance, whether a switch achieves its function in a time- or spacedivided manner is not relevant from a performance perspective, as one can theoretically map either implementation to the other, resulting in the same external behavior. In the following overview of packet-switch architectures, the main focus will be on the queuing discipline. Of course, it can be argued that the choice of queuing discipline is also an implementation issue, and from a high-level point of view—regarding the switch as a black box that moves data from A to B—this is certainly true. However, for the purpose of this dissertation, the correct abstraction level is that of the internal switch architecture, and thus the queuing discipline, because this is the determining factor of switch performance. Moreover, in this overview, we shall not concern ourselves with specific hardware implementation details of these architectures.

The remainder of this chapter is organized as follows: In Section 2.1.1 we distinguish between

blocking and non-blocking architectures. Section 2.2 briefly reviews a not so useful architecture with no buffers at all, merely as a reference. Sections 2.3 and 2.4 treat the classic inputand output-queued architectures respectively. The principle of shared queuing is reviewed in Section 2.5. Because of the resurgent interest in input-queued architectures, a large number of papers on this topic have been published in recent years. Given the significance of the results of this research, and as there is no comprehensive overview available in the literature today, Section 2.6 provides a comprehensive survey of this new generation of input-queued architectures. The latest development trends in the field are towards new combined input- and output-queued (CIOQ) architectures, which will be surveyed in Section 2.7. Finally, in Section 2.8 we discuss the merits and drawbacks of the most widely used architectures today, and summarize the key points that can be gleaned from the overview presented.

### 2.1.1 Blocking and non-blocking switch architectures

In packet-switching architectures two forms of *blocking* can be distinguished. First, owing to the statistical, non-deterministic nature of packet arrivals at the switch, more than one packet destined for the same output may arrive at the inputs simultaneously. Of these packets only one can be forwarded to the output, while the others have to wait. Therefore, the switch has to be equipped with buffers to accommodate packets that cannot be forwarded immediately. This inevitable form of blocking is called *output contention*. The second form of blocking is related to the internal structure of a packet switch, e.g., in a multi-stage switch contention for fabric-internal links may occur, even among packets destined for different output ports. Architectures that exhibit this behavior, e.g. Banyan networks, are referred to as *blocking*. Clearly, this property is undesirable, as it has highly adverse effects on switch performance.<sup>1</sup>

A switch architecture is called *non-blocking* when it satisfies the requirement that an arriving packet destined for any output to which no other packets are destined can be forwarded immediately, regardless of the destinations of all other arriving packets. From here on, we will focus on this type of switch architecture.

### 2.1.2 Sequence-preserving

Depending on the switch-fabric application, there may be a strict requirement regarding the order in which packets leave the switch. In particular, certain applications, such as ATM, impose the strict requirement that packets belonging to the same flow *must* be delivered in the order they arrived in. For the switch, this means that sequence of packets belonging to a given combination of input port, output port, and virtual lane must be maintained.

## 2.1.3 Single-stage vs. multi-stage switches

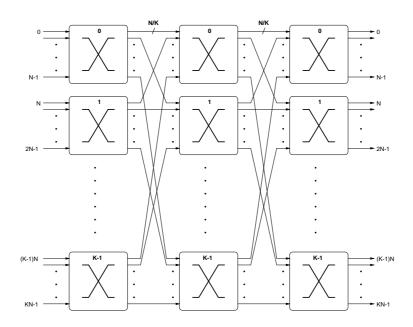

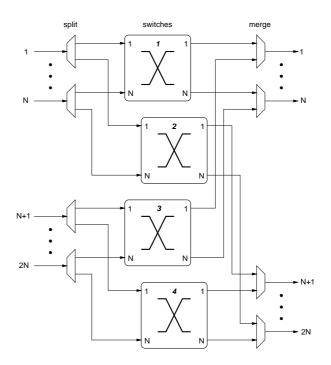

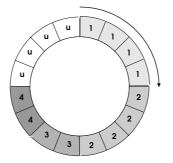

Fig. 2.1 depicts a  $KN \times KN$  Benes multistage switch fabric consisting of three stages of  $K N \times N$  switches each. For large networks, the multistage approach is much cheaper in terms of the required number of switch elements than single-stage port expansion. In general, for

<sup>&</sup>lt;sup>1</sup>For Banyan networks, the blocking property can be avoided by preceding the Banyan with a Batcher bi-tonic sort network. The *Starlite* switch [Huang84] was the first to employ the Batcher-Banyan self-routing structure.

an  $M \times M$  fabric, with M = KN, KS switch elements are required for an S-stage fabric compared to  $K^2$  for a single-stage fabric (see Section 6.3.2).

Figure 2.1: A  $KN \times KN$  multistage network consisting of  $3K N \times N$  switch elements.

We will only consider single-stage architectures here. Single-stage architectures have a strong performance advantage over multi-stage architectures, but inherently are not as scalable. Therefore, as bandwidth demands continue to rise, there will be a growing need for multi-stage fabrics because these can scale to many times more ports than any single-stage architecture can. However, we consider the multi-stage problem as partly orthogonal—after all, a multi-stage fabric is a cascade of single-stage switches. Still, the extension of a given single-stage architecture to multi-stage is far from trivial. To convey the complexity of making multi-stage fabrics work, let us briefly mention the main issues:

- Network topology: which topology—e.g. Benes, Banyan, BMIN, Hypercube, Torus, etc.—is the right one for a given application?

- Performance: both in terms of delay because more stages means more latency and throughput because multi-stage fabrics are often internally blocking owing to a combination of the fabric's interconnection topology, static routing, or higher-order HoL blocking [Jurczyk96].

- Fabric-internal routing: static routing is easy to implement, but leads to poor performance under unfavorable traffic patterns because it cannot adapt to congestion situations, whereas adaptive routing can improve performance, but is expensive to implement and may lead to out-of-order delivery. Either source routing or per-hop look-up is required.

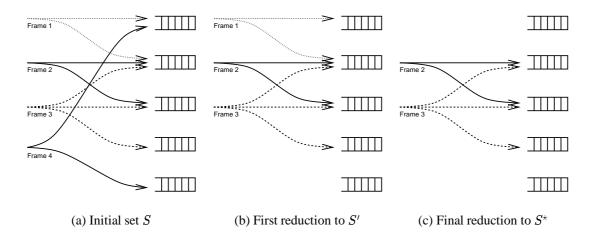

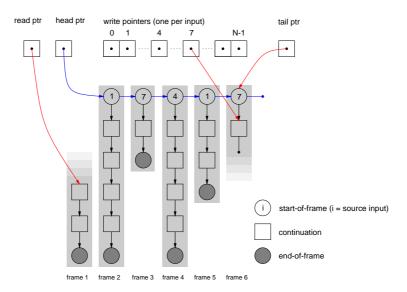

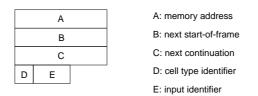

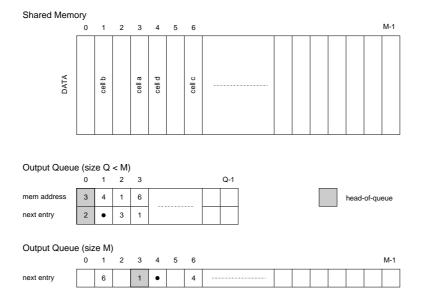

- Flow control: to maintain performance, prevent higher-order HOL blocking, and guarantee fabric-internal losslessness, proper flow control is required. To obtain maximum performance, global end-to-end flow control may be necessary, which presents significant scaling problems.