RZ 3921 Physical Sciences (# ZUR1705-003) 2 pages 05/03/2017

# **Research Report**

# Monolithic Integration of InAlAs/InGaAs Quantum-Well on InP-OI Micro-substrates on Si for Infrared Light Sources

Y. Baumgartner, B. Mayer, M. Sousa, D. Caimi, K. Moselund, L. Czornomaz

IBM Research – Zurich 8803 Rüschlikon Switzerland

The final version of this article has been published by IEEE:

Y. Baumgartner, B. Mayer, M. Sousa, D. Caimi, K. Moselund and L. Czornomaz, "Monolithic integration of InAlAs/InGaAs quantum-well on InP-OI micro-substrates on Si for infrared light sources," *Proc.2017 IEEE 14th International Conference on Group IV Photonics (GFP)*, Berlin, 2017, pp. 173-174. © 2017 IEEE. doi: 10.1109/GROUP4.2017.8082252

#### LIMITED DISTRIBUTION NOTICE

This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies (e.g., payment of royalties). Some reports are available at http://domino.watson.ibm.com/library/Cyberdig.nsf/home.

#### Monolithic Integration of InAIAs/InGaAs Quantum-Well on InP-OI Micro-substrates on Si for Infrared Light Sources

Y. Baumgartner<sup>a</sup>, B. Mayer<sup>a</sup>, M. Sousa<sup>a</sup>, D. Caimi<sup>a</sup>, K. Moselund<sup>a</sup>, L. Czornomaz<sup>a</sup>.

<sup>a</sup> IBM Research GmbH, Säumerstrasse 4, CH-8803 Rüschlikon, Switzerland.

Abstract - We demonstrate for the first time that InAIAs/InGaAs QW can be selectively grown on micron-sized InP-OI substrates, obtained by selective epitaxy in empty oxide cavities on Si. The concept, material and optical characterizations are presented, paving the way towards integrated light sources for infrared applications.

#### I. Introduction

Using optical interconnects with Silicon Photonics (SiPh) is expected to be the ultimate solution to boost the cost-efficiency and bandwidth of data centres [1]. However on-chip light sources coupled to SiPh are missing owing to the difficulty to integrate III-V gain materials on Si. Selective epitaxy of III-V compounds on large Si wafers is the most competitive approach to integrate such light sources, assuming that the crystalline quality of the III-V can be further improved [2].

Selective epitaxy in oxide cavities was previously used to demonstrate III-V/SiGe CMOS circuits, III-V nanowires and III-V heterojunction Tunnel FETs on Si [3,4,5,6]. Recently this concept was extended to integrate GaAs virtual substrates on SOI wafers for integrated light sources [7]. Here we further develop this concept and demonstrate the integration of InAIAs/InGaAs quantum-well (QW) on local InP micro-substrates on SOI. Our results show that III-V gain material can be used for III-V/Si lasers.

#### II. Concept

The large lattice mismatch of III-V compounds with Si and the change of polarity at the substrate interface restrict the use of III-V materials for integrated devices on Si, due to a high density of dislocations, antiphase domains and stacking faults in the III-V layer. Recently one dimensional defect filtering via aspect ratio trapping was used to obtain hybrid opticallypumped distributed feedback lasers on Si [8].

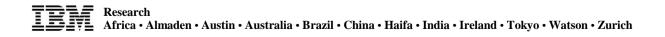

In the present work we further improve the material quality by integrating micron-sized InP islands on Si wafers using selective epitaxy in empty SiO<sub>2</sub> cavities. This growth technique typically restricts most defects in the first nanometres of the III-V layer [9], thanks to an efficient defect filtering in many directions. Empty SiO<sub>2</sub> cavities are obtained using CMOS-compatible processes and materials, as shown in Fig. 1. The cavities contain 1) a small crystalline Si seed, 2) an arbitrarily defined geometry which shapes the growing III-V crystal, and 3) openings to allow the

metalorganic precursors to enter the cavity. Micron-sized InP substrates are grown by metal-organic chemical vapor deposition (MOCVD) within the cavities. After stripping the top oxide of the cavities, the surface of InP islands is used for the overgrowth of III-V heterostructures. We chose as a model system to grow a lattice-matched InAIAs/InGaAs stack containing 3 QW.

## III. Results and discussion

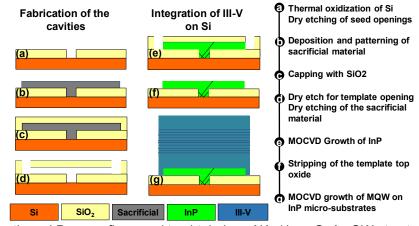

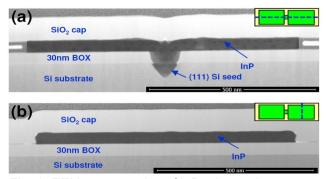

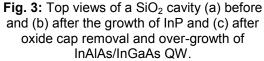

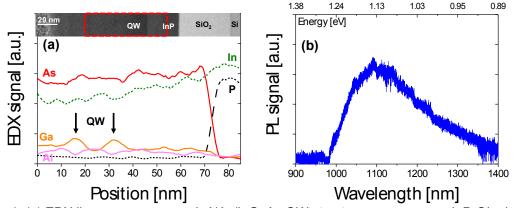

Transmission Electron Microscopy (TEM) performed after the growth of InP within the cavities are shown on Fig. 2. Such InP-on-Insulator (InP-OI) micro-substrates can be used for the integration of other III-V materials on Si. SEM images of Fig. 3 show the cavity before (a) and after (b) the growth of InP. Fig. 3(c) illustrates an overgrown InAIAs/InGaAs QW stack on InP. The surface morphology and roughness indicates that the layer might contain some crystalline defects, originating either from strain relaxation the targeted in In<sub>0.52</sub>AIAs/In<sub>0.53</sub>GaAs stack or from the InP-OI micro-substrates. As compared with regular growth on InP wafer, selective epitaxy of ternaries is challenging owing to varying loading factor across the wafer and fluctuating diffusion length of the group-III atoms on the surrounding SiO<sub>2</sub>. EDX line-scans of Fig. 4(a) reveal the presence of the InGaAs QW and InAIAs barriers and a sharp interface with the InP-OI microsubstrate. PL at room-temperature was observed, with a central wavelength at 1090 nm (Fig. 4(b)). Improved process conditions for the QW growth – or the integration of more complex III-V guaternary heterostructures on the InP-OI micro-substrates - will allow providing gain at higher wavelengths.

## IV. Conclusions

Using selective epitaxy in empty SiO<sub>2</sub> cavities, we demonstrate the monolithic integration of InP-OI micro-substrates on Si, which can be used to overgrow other III-V stacks. We show a room-temperature PL signal from an overgrown InAIAs/InGaAs heterostructure, paving the way for cost-efficient and CMOS-compatible laser sources for infrared applications.

#### V. Acknowledgements

Fruitful discussions with Prof. Jérôme Faist and support by the BRNC OpTeam are acknowledged. This project has received funding from the EU-H2020 research and innovation programme under grant No 688003, 688172 and 688544.

#### References

- [1] S. Assefa, et al., IEDM, (2012).

- [2] J. Bowers, et al., OFC, (2017).

- [3] L. Czornomaz, et al., VLSI Technology, (2015).

- [4] L. Czornomaz, et al., VLSI Technology, (2016).

- [5] H. Schmid, et al., Appl. Phys. Lett., (2015).

- [6] D. Cutaia, et al., VLSI Technology, (2016).

- [7] B. Mayer, et al., CLEO, (2017).

- [8] Z. Wang, et al., Nat. Photonics, 9(12):837\_842, (2015).

- [9] L. Czornomaz, PhD Thesis, Chapter 2, (2016).

- [10] H. Hahn, et al., DRC, (2017).

**Fig. 1:** Schematic and Process flow used to obtain In<sub>0.52</sub>AlAs/ In<sub>0.53</sub>GaAs QW structures on InP-OI micro-substrates.

Fig. 2: TEM cross section of InP micro-substrates on Si (a) along and (b) perpendicular to the growth direction [9].

Fig. 4: (a) EDX line-scan across an InAIAs/InGaAs QW structures grown on an InP-OI microsubstrate. Inset: TEM image of the QW stack - analyzed area in red. (b) PL signal from one overgrown QW structure acquired at room temperature.